Leaderboard

Popular Content

Showing content with the highest reputation on 09/22/2018 in all areas

-

I just rearranged the nodes that the devices are disconnected instead of switching automatically. In a previous post, you said that your mainboard has only one output, since there are already two layouts without auto switching, I would suggest trying layout 11 and 50. Layout-id 1 is for 5.1 speakers and you have 2 non-functioning devices. If layout 11 or 50 does not meet your requirements, I can create a new layout and upload it so that vit9696/vandroiy can add it to the ALC source.4 points

-

Usb3 in porta usb2 va bene, ma le porte usb3 sono sdoppiate (HSxy + SSxy), quindi ti serve una chiavetta usb2 per quelle2 points

-

Esatto, grazie ragazzi! Sempre al TOP e lo dico davvero Inviato dal mio ONEPLUS A6003 utilizzando Tapatalk2 points

-

Buono. Ora non ti resta che mappare le porte usb per togliere la patch per il port limit.2 points

-

Hi KGP-iMacPro, Point well made. I won't return it/RMA, I promise! Now, tell me (& others) what do you want me to further test this Asus TB3 adapter, ok ?2 points

-

@augustopaulo, I rather think the opposite! This adaptor or your current configuration might be a unique opportunity to shed new light onto the entire TB Hackintosh story.. we just don't know yet why and in which way. The only thing I would like to ask you: please never return it to the manufacturer until we deeply investigated cause and effects of your recent discovery.. Generally I don't think that it is a good idea to mix things between Windows and macOS.. Don't forget that we are dealing with UEFI.. thus specific settings under some certain operating system might affect the adopters functionality in the other operating system. Me myself many times I even reached to a situation where the removal and replugging of the adopter was the only possibility to make the adopter work again under any system. Also don't be scared that the adopter is not fully functional and reveals errors.. While we might miss some of your implementations and functionalities you might miss some of our implementations and functionalities.. The fusion and merge of our different implementations, results, discoveries, and experiences might lead to some breakthrough though.. We have to wait and see.. Thus please, once more don't request any RMA for the adopter. It is a 50$ investment that could change many things! I rather encourage you to purchase a second adopter to see whether or not you would be able to replicate the same effects with an else unchanged system configuration.2 points

-

il supporto nvram è dato dai driver uefi di osxaptioFix quello che da supporto nvram è il 3 versione normale o V2 hanno perso il supporto da kabylake e anche skylake da quando vennero rilasciati i nuovi bios per supportare la nuova generazione di cpu Detto questo...personalmente consiglio si usare aptiomemory2 points

-

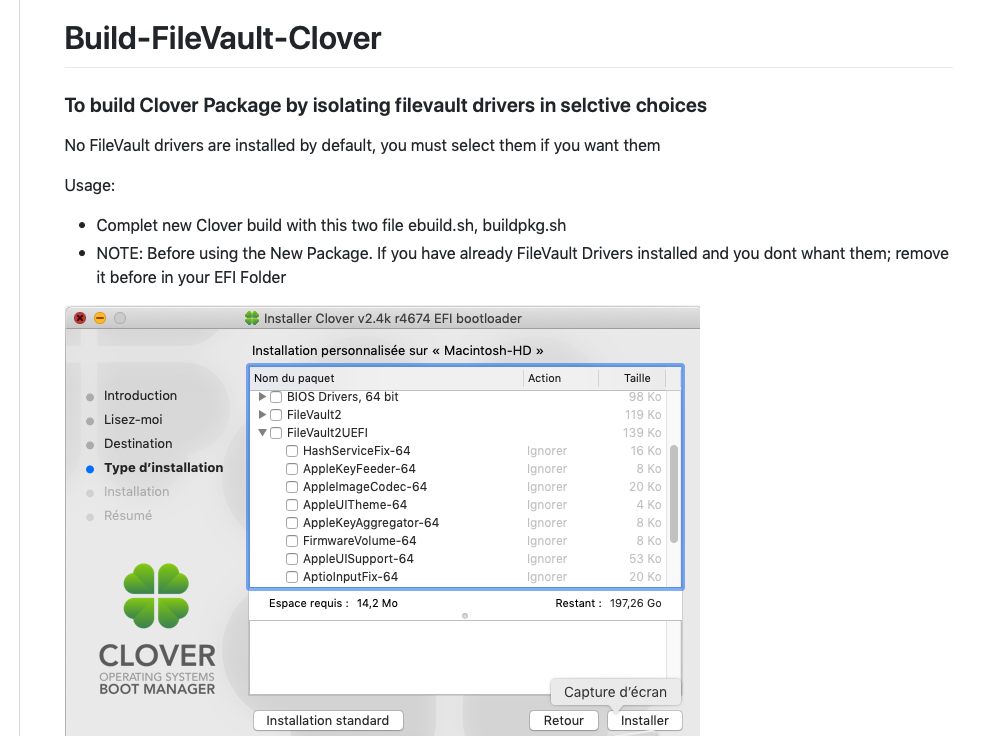

Thank you for being part of the solution chris. this is what most users where asking for. a clear separation of what what is what. at least now the end user knows that those drivers are different to the general ones. as for EULA we know it is open source slice. its just small contributions like this that make the project better. that is what open source is.2 points

-

2 points

-

Direi che di cambiamenti ne hai fatti dalla Clover iniziale ..... Buon Hack1 point

-

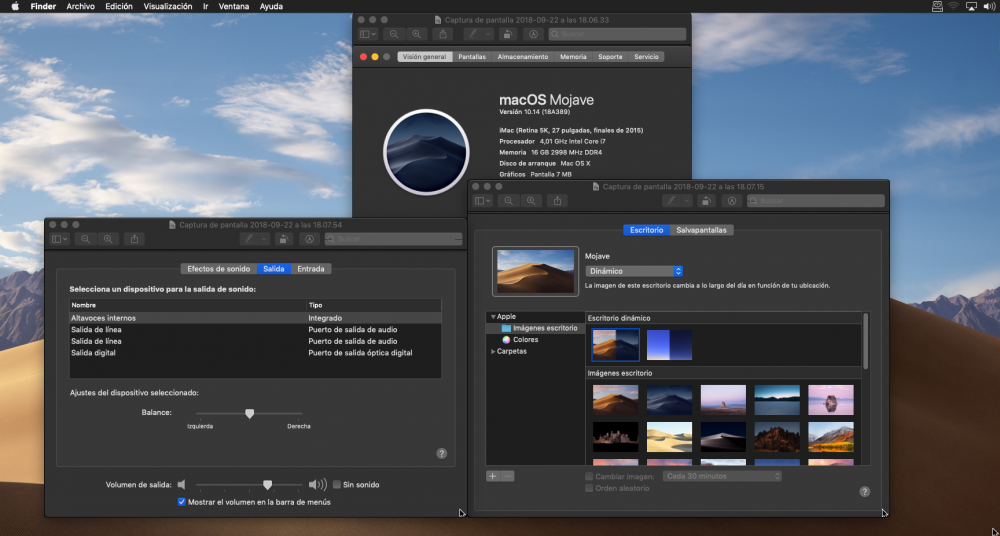

Primero deberias publicar las especificaciones de tu Hardware y lo que utilizas para el arranque. Yo utilizo la ultima version de Clover y las ultimas compilaciones de Lilu, AppleALC, WhateverGreen y VirtualSMC (este ultimo en lugar de FakeSMC y SMChelper.efi). Tambien en DriversUEFI64 los mas actuales. Todo ello me ha permitido instalar directamente desde 10.13.6 a Mojave nativamente y sin problemas. He podido arrancar con Nvidia e Intel Skylake sin aceleracion por falta de Controladores para Nvidia. He arrancado tambien con HD530 Skylake (sin Grafica Nvidia) con aceleracion y sin problemas. Suerte.1 point

-

1 point

-

I you select UEFI Only drivers FileVault2 for Legacy(x64) not appears on choice Of course If you are deselect UEFI Only the Drivers x64 filevault2 is selectable1 point

-

diciamo che si hanno notizie contrastanti, personalmente il TRIM lo lascio attivo nel config1 point

-

sysprefs doesnt change the click behaviour for me. more detailed issue: physical clicks work about 30% of the time. The rest either the mouse button up or the mouse button down event is not registered in a timely manner. takes 1-3seconds to fix itself. * physical clicks are not registered (nothing happens), this only happens after at least one successful click in the past few seconds * a drag and drop / highlighting is not released and will continue even without any button pressed -> will be freed after a short amount of time after the actual button up event * hammering the physical click will make it worse (counter-intuitive ;-) ) * taps work like intended, dont seem to interrupt the physical click "timer" i have the issue on two different dell xps 15 models, so i doubt it has anything to do with faulty hardware (and it works well with voodoops2)1 point

-

Purtroppo a ora non avrei soluzioni e idee.. guardo un po'..nel caso ti faccio risapere1 point

-

hai già ssdt nella mia ultima clover... e le proprietà iniettate sono ok e tutte caricate...1 point

-

KextUpdater no chequea la carpeta kexts de tu EFI (notarás que no la monta para revisar), asumo que extrae la lista de un bootlog de Clover o con kextstat, donde se detalla la versión de cada kext cargado durante el arranque. La versión de Slice tiene una numeración distinta de la de kozlek asi que KU no las mezclaría supongo, pero la de rehabman no se que tiene ni que versiones usa. Creo que es prácticamente la de kozlek con mínimos cambios.1 point

-

1 point

-

1 point

-

1 point

-

1 point

-

1 point

-

tutto normale...le ventole vengono regolate da osx e dal relativo bios della video1 point

-

Prova con questo e rifai l'ioreg. Tieni sempre una EFI funzionante a portata di mano. DSDT.aml.zip Edit: Va messo in EFI/CLOVER/ACPI/patched1 point

-

AptioInputFix serve solo se usi Filevault altrimenti lo puoi levare quello che descrivi delle ventole secondo me è il comportamento normale che deve avere all'accensione shkigva e rad4200 sono superati, ora con le ultime versioni di LILU e WEG (WahtEverGreen) dovrebbe andare tutto bene senza custom flag1 point

-

let me think and come back to you with certain proposals.. ideas and input of others of course also would be highly welcome at this place.. The most interesting test for now would be if you could replicate the same effects also with a second different adopter. This would limit the open variables and might shed light onto the open question if the miracle is really caused by the current, special adopter or rather by something else in your overall system configuration.1 point

-

1 point

-

esattamente il consiglio messo da @foskvs il solo AptioMemoryFix, se poi la NVRAM non lavora installi anche gli rc script ma mi pare strano che in UEFI puro non ti lavori la NVRAM, ma per saperlo vedi qui1 point

-

1 point

-

Prova AptioMemoryFix.efi al posto di OsxAptioFix2 (meglio se testi da usb) togliendo emuvariable.1 point

-

Hasta ahora no he tenido problemas actualizando el FakeSMC a mano, primero borro el viejo y luego copio el nuevo. Quizá la nueva no es la misma versión que ya tienes (hay de distintos desarrolladores: Slice, Kozlek, rehabman) y tiene algo distinto que no es compatible con tu hardware.1 point

-

Trial and error, try without, see what happens, been a while since I was legacy1 point

-

1 point

-

Ok, try this. Not sure if it works, maybe a device needs to be removed. AppleALC.kext.zip1 point

-

Great Job These file modifications are very interesting. For beginners, I think it would be easier if FV2 files are not checked by default, in my opinion.1 point

-

Yes , yesterday night I compiled a SSDT with appropriate parts from this DSDT and no miracle... ( even with adjusting thunderbolt settings in bios)1 point

-

yup. nevermind. got the same thing after i removed older SDKs. thanks1 point

-

Seems that @augustopaulo performs some DSDT patching... Now the question is where all this comes from? Scope (_GPE) { OperationRegion (TCOS, SystemIO, 0x0464, 0x02) Field (TCOS, ByteAcc, NoLock, WriteAsZeros) { Offset (0x01), , 1, DSCI, 1 } Method (_L01, 0, NotSerialized) // _Lxx: Level-Triggered GPE { Sleep (0xC8) Store (One, IO80) Sleep (0x0A) Store (Zero, Local1) If (LEqual (\_SB.PCI0.BR1A.PMEP, One)) { Store (\_SB.PCI0.BR1A.PMEH (0x09), Local0) } Else { Store (\_SB.PCI0.BR1A.HPEH (0x09), Local0) } If (LEqual (ToInteger (TBRP), 0x22)) { Store (0xFF, Local0) Store (One, Local1) } If (LNotEqual (Local0, 0xFF)) { Store (One, Local1) Notify (\_SB.PCI0.BR1A.UPSB, Local0) Notify (\_SB.PCI0.BR1A.H001, Local0) Notify (\_SB.PCI0.BR1A.H002, Local0) Notify (\_SB.PCI0.BR1A.H003, Local0) Notify (\_SB.PCI0.BR1A.H004, Local0) Notify (\_SB.PCI0.BR1A.H005, Local0) Notify (\_SB.PCI0.BR1A.H006, Local0) Notify (\_SB.PCI0.BR1A.H007, Local0) } } } Device (BR1A) { Name (_ADR, 0x00010000) // _ADR: Address OperationRegion (MCTL, SystemMemory, 0xE001A188, 0x04) Field (MCTL, ByteAcc, NoLock, Preserve) { , 3, HGPE, 1, , 7, , 8, , 8 } Method (_INI, 0, NotSerialized) // _INI: Initialize { Store (One, HGPE) Return (Zero) } Name (_HPP, Package (0x04) // _HPP: Hot Plug Parameters { 0x08, 0x40, One, Zero }) Name (SHPC, 0x40) Name (SPDS, 0x40) Name (MRLS, Zero) Name (CCOM, 0x10) Name (SPDC, 0x08) Name (MRLC, 0x04) Name (SPFD, 0x02) Name (SABP, One) Name (SPOF, 0x10) Name (SPON, 0x0F) Name (ALMK, 0x1C) Name (ALON, One) Name (ALBL, 0x02) Name (ALOF, 0x03) Name (PLMK, 0x13) Name (PLON, 0x04) Name (PLBL, 0x08) Name (PLOF, 0x0C) Name (HPEV, 0x0F) OperationRegion (PPA4, PCI_Config, Zero, 0x0100) Field (PPA4, ByteAcc, NoLock, Preserve) { Offset (0xA0), , 4, LDIS, 1, Offset (0xA2), Offset (0xA4), ATBP, 1, , 1, MRSP, 1, ATIP, 1, PWIP, 1, HPSR, 1, HPCP, 1, , 12, PSNM, 13, ABIE, 1, PFIE, 1, MSIE, 1, PDIE, 1, CCIE, 1, HPIE, 1, SCTL, 5, Offset (0xAA), SSTS, 7, Offset (0xAB), Offset (0xB0), Offset (0xB2), PMES, 1, PMEP, 1, Offset (0xB4) } Method (ATID, 0, NotSerialized) { Return (And (SCTL, 0x03)) } Method (PWID, 0, NotSerialized) { Return (ShiftRight (And (SCTL, 0x0C), 0x02)) } Method (PWCC, 0, NotSerialized) { Return (ShiftRight (And (SCTL, 0x10), 0x04)) } Method (ABPS, 1, NotSerialized) { If (LEqual (Arg0, One)) { Or (SSTS, One, SSTS) } Return (And (SSTS, One)) } Method (PFDS, 1, NotSerialized) { If (LEqual (Arg0, One)) { Or (SSTS, 0x02, SSTS) } Return (ShiftRight (And (SSTS, 0x02), One)) } Method (MSCS, 1, NotSerialized) { If (LEqual (Arg0, One)) { Or (SSTS, 0x04, SSTS) } Return (ShiftRight (And (SSTS, 0x04), 0x02)) } Method (PDCS, 1, NotSerialized) { If (LEqual (Arg0, One)) { Or (SSTS, 0x08, SSTS) } Return (ShiftRight (And (SSTS, 0x08), 0x03)) } Method (CMCS, 1, NotSerialized) { If (LEqual (Arg0, One)) { Or (SSTS, 0x10, SSTS) } Return (ShiftRight (And (SSTS, 0x10), 0x04)) } Method (MSSC, 1, NotSerialized) { If (LEqual (Arg0, One)) { Or (SSTS, 0x20, SSTS) } Return (ShiftRight (And (SSTS, 0x20), 0x05)) } Method (PRDS, 1, NotSerialized) { If (LEqual (Arg0, One)) { Or (SSTS, 0x40, SSTS) } Return (ShiftRight (And (SSTS, 0x40), 0x06)) } Method (OSHP, 0, NotSerialized) { Store ("SSTS", SSTS) Store (Zero, HGPE) } Method (HPCC, 1, NotSerialized) { Store (SCTL, Local0) Store (Zero, Local1) If (LNotEqual (Arg0, Local0)) { Store (Arg0, SCTL) While (LAnd (LNot (CMCS (Zero)), LNotEqual (0x64, Local1))) { Sleep (0x02) Add (Local1, 0x02, Local1) } CMCS (One) } } Method (ATCM, 1, NotSerialized) { Store (SCTL, Local0) And (Local0, ALMK, Local0) If (LEqual (Arg0, One)) { Or (Local0, ALON, Local0) } If (LEqual (Arg0, 0x02)) { Or (Local0, ALBL, Local0) } If (LEqual (Arg0, 0x03)) { Or (Local0, ALOF, Local0) } HPCC (Local0) } Method (PWCM, 1, NotSerialized) { Store (SCTL, Local0) And (Local0, PLMK, Local0) If (LEqual (Arg0, One)) { Or (Local0, PLON, Local0) } If (LEqual (Arg0, 0x02)) { Or (Local0, PLBL, Local0) } If (LEqual (Arg0, 0x03)) { Or (Local0, PLOF, Local0) } HPCC (Local0) } Method (PWSL, 1, NotSerialized) { Store (SCTL, Local0) If (Arg0) { And (Local0, SPON, Local0) } Else { Or (Local0, SPOF, Local0) } HPCC (Local0) } Method (_OST, 3, Serialized) // _OST: OSPM Status Indication { Switch (And (Arg0, 0xFF)) { Case (0x03) { Switch (ToInteger (Arg1)) { Case (Package (0x04) { 0x80, 0x81, 0x82, 0x83 } ) { If (LNot (PWCC ())) { PWCM (One) Store (One, ABIE) } } } } } } Method (EJ0L, 1, NotSerialized) { Store (0xFF, IO80) Store (SCTL, Local0) If (LNotEqual (ATID (), One)) { And (Local0, ALMK, Local0) Or (Local0, ALBL, Local0) } HPCC (Local0) Store (SCTL, Local0) Or (Local0, SPOF, Local0) HPCC (Local0) Store (SCTL, Local0) Or (Local0, PLOF, Local0) HPCC (Local0) Store (SCTL, Local0) Or (Local0, ALOF, Local0) HPCC (Local0) } Method (PMEH, 1, NotSerialized) { If (And (HPEV, SSTS)) { If (ABPS (Zero)) { ABPS (One) Sleep (0xC8) } } Return (0xFF) } Method (HPEH, 1, NotSerialized) { If (LNot (HPCP)) { Return (0xFF) } Sleep (0x64) Store (Zero, CCIE) If (And (HPEV, SSTS)) { Store (0xFD, IO80) Sleep (0x0A) Store (PPXH (Zero), Local0) Return (Local0) } Else { Return (0xFF) } Store (0xFC, IO80) Sleep (0x0A) } Method (PPXH, 1, NotSerialized) { Sleep (0xC8) If (ABPS (Zero)) { If (LNot (PRDS (Zero))) { Store (One, LDIS) PWSL (Zero) PWCM (0x03) If (LEqual (MSSC (Zero), MRLS)) { ATCM (0x02) } Else { ATCM (0x03) } ABPS (One) Sleep (0xC8) Return (0xFF) } Store (Zero, ABIE) ABPS (One) Sleep (0xC8) If (PWCC ()) { ATCM (0x02) Sleep (0x0258) Store (0x0258, Local0) ABPS (One) While (LNot (ABPS (Zero))) { Sleep (0xC8) Add (Local0, 0xC8, Local0) If (LEqual (0x1388, Local0)) { Store (One, ABIE) ATCM (0x03) PWCM (0x02) Sleep (0x0258) Store (Zero, LDIS) PWSL (One) Sleep (0x01F4) If (LNot (PFDS (Zero))) { PWCM (One) Store (Zero, Local1) Store (One, ABIE) } Else { PWSL (Zero) PWCM (0x03) ATCM (One) Store (One, LDIS) Store (0x03, Local1) Store (One, ABIE) } ABPS (One) Sleep (0xC8) Return (Local1) } } Return (0xFF) } Else { ATCM (0x02) Sleep (0x0258) Store (0x0258, Local0) ABPS (One) Sleep (0xC8) While (LNot (ABPS (Zero))) { Sleep (0xC8) Add (Local0, 0xC8, Local0) If (LEqual (0x1388, Local0)) { ABPS (One) ATCM (0x03) PWCM (0x02) Sleep (0xC8) Store (One, ABIE) Store (One, LDIS) PWCM (0x03) Return (0x03) } } PWCM (One) ABPS (One) Sleep (0xC8) Store (One, ABIE) Return (0xFF) } } If (PFDS (Zero)) { PFDS (One) PWSL (Zero) PWCM (0x03) ATCM (One) Store (One, LDIS) Return (0x03) } If (PDCS (Zero)) { PDCS (One) If (LNot (PRDS (Zero))) { PWSL (Zero) PWCM (0x03) If (LEqual (MSSC (Zero), MRLS)) { ATCM (0x02) } Else { ATCM (0x03) } Store (One, LDIS) Return (0xFF) } Else { Store (Zero, LDIS) ABPS (One) Sleep (0xC8) Store (One, ABIE) Sleep (0xC8) Return (Local1) } } Return (0xFF) } Method (SNUM, 0, Serialized) { Store (PSNM, Local0) Return (Local0) } Device (UPSB) { Name (_ADR, Zero) // _ADR: Address Device (DSB0) { Name (_ADR, Zero) // _ADR: Address Method (_DSM, 4, NotSerialized) // _DSM: Device-Specific Method { If (LEqual (Arg2, Zero)) { Return (Buffer (One) { 0x03 }) } Return (Package (0x02) { "PCIHotplugCapable", Zero }) } Device (NHI0) { Name (_ADR, Zero) // _ADR: Address Name (_STR, Unicode ("Thunderbolt")) // _STR: Description String Method (_DSM, 4, NotSerialized) // _DSM: Device-Specific Method { If (LEqual (Arg2, Zero)) { Return (Buffer (One) { 0x03 }) } Return (Package (0x08) { "AAPL,slot-name", "Built In", "name", "Thunderbolt 3 Controller", "device_type", Buffer (0x0E) { "Thunderbolt 3" }, "model", Buffer (0x27) { "Thunderbolt 3 NHI Alpine Ridge 4C 2015" } }) } } } Device (DSB1) { Name (_ADR, 0x00010000) // _ADR: Address Device (UPS0) { Name (_ADR, Zero) // _ADR: Address } } Device (DSB2) { Name (_ADR, 0x00020000) // _ADR: Address Method (_DSM, 4, NotSerialized) // _DSM: Device-Specific Method { If (LEqual (Arg2, Zero)) { Return (Buffer (One) { 0x03 }) } Return (Package (0x02) { "PCIHotplugCapable", Zero }) } Device (XHC2) { Name (_ADR, Zero) // _ADR: Address Method (_DSM, 4, NotSerialized) // _DSM: Device-Specific Method { If (LEqual (Arg2, Zero)) { Return (Buffer (One) { 0x03 }) } Return (Package (0x0E) { "AAPL,slot-name", "Built In", "name", "USB 3.1 Controller", "device_type", Buffer (0x13) { "USB 3.1 Controller" }, "model", Buffer (0x35) { "Intel Corporation, USB 3.1 Controller [Alpine Ridge]" }, "USBBusNumber", Zero, "AAPL,xhci-clock-id", One, "UsbCompanionControllerPresent", One }) } } } Device (DSB4) { Name (_ADR, 0x00040000) // _ADR: Address Device (UPS0) { Name (_ADR, Zero) // _ADR: Address } } } Device (H001) { Name (_ADR, One) // _ADR: Address Method (_SUN, 0, NotSerialized) // _SUN: Slot User Number { Return (SNUM ()) } } Device (H002) { Name (_ADR, 0x02) // _ADR: Address Method (_SUN, 0, NotSerialized) // _SUN: Slot User Number { Return (SNUM ()) } } Device (H003) { Name (_ADR, 0x03) // _ADR: Address Method (_SUN, 0, NotSerialized) // _SUN: Slot User Number { Return (SNUM ()) } } Device (H004) { Name (_ADR, 0x04) // _ADR: Address Method (_SUN, 0, NotSerialized) // _SUN: Slot User Number { Return (SNUM ()) } } Device (H005) { Name (_ADR, 0x05) // _ADR: Address Method (_SUN, 0, NotSerialized) // _SUN: Slot User Number { Return (SNUM ()) } } Device (H006) { Name (_ADR, 0x06) // _ADR: Address Method (_SUN, 0, NotSerialized) // _SUN: Slot User Number { Return (SNUM ()) } } Device (H007) { Name (_ADR, 0x07) // _ADR: Address Method (_SUN, 0, NotSerialized) // _SUN: Slot User Number { Return (SNUM ()) } } OperationRegion (PXCS, PCI_Config, Zero, 0xE0) Field (PXCS, AnyAcc, NoLock, Preserve) { VDID, 32, Offset (0x54), , 6, HPCE, 1, Offset (0x5A), ABPX, 1, , 2, PDCX, 1, , 2, PDSX, 1, Offset (0x5B), Offset (0x60), Offset (0x62), PMEX, 1, Offset (0xDC), , 31, PMCS, 1 } Method (DEVS, 0, NotSerialized) { If (LEqual (VDID, 0xFFFFFFFF)) { Return (Zero) } Else { Return (0x0F) } } Method (HPME, 0, Serialized) { If (PMEX) { Store (0xC8, Local0) While (Local0) { Store (One, PMEX) If (PMEX) { Decrement (Local0) } Else { Store (Zero, Local0) } } Store (One, PMCS) } } Method (_PRW, 0, NotSerialized) // _PRW: Power Resources for Wake { Return (GPRW (0x09, 0x04)) } Method (_PRT, 0, NotSerialized) // _PRT: PCI Routing Table { If (PICM) { Return (AG22) } Return (PG22) } Device (D07C) { Name (_ADR, 0xFFFF) // _ADR: Address } } These DSDT code snippets roughly contain the entire TB ACPI definition.. Some difference with SSDT-9.aml are the actual _GPE and method _INI implementation of BR1A , which however seem to be also part of there original Asus X99 Deluxe II DSDT.aml, while the respective iMac Pro SSDT-9.aml implementations Scope (\_GPE) { Method (_L32, 0, NotSerialized) // _Lxx: Level-Triggered GPE { If (LNot (OSDW ())) { If (LEqual (\_SB.PC01.BR1A.POC0, One)) { Return (Zero) } Sleep (0x0190) If (LEqual (\_SB.PC01.BR1A.WTLT (), One)) { \_SB.PC01.BR1A.ICMS () } Else { } If (\_SB.PC01.BR1A.UPMB) { Store (Zero, \_SB.PC01.BR1A.UPMB) Sleep (One) } Else { } \_SB.PC01.BR1A.CMPE () } ElseIf (LEqual (\_SB.GGII (0x01030012), One)) { \_SB.SGII (0x01030012, Zero) } Else { \_SB.SGII (0x01030012, One) } \_SB.PC01.BR1A.UPSB.AMPE () Return (Zero) } Return (One) } Name (EICM, Zero) Name (R020, Zero) Name (R024, Zero) Name (R028, Zero) Name (R02C, Zero) Name (R118, Zero) Name (R119, Zero) Name (R11A, Zero) Name (R11C, Zero) Name (R120, Zero) Name (R124, Zero) Name (R128, Zero) Name (R12C, Zero) Name (R218, Zero) Name (R219, Zero) Name (R21A, Zero) Name (R21C, Zero) Name (R220, Zero) Name (R224, Zero) Name (R228, Zero) Name (R22C, Zero) Name (R318, Zero) Name (R319, Zero) Name (R31A, Zero) Name (R31C, Zero) Name (R320, Zero) Name (R324, Zero) Name (R328, Zero) Name (R32C, Zero) Name (R418, Zero) Name (R419, Zero) Name (R41A, Zero) Name (R41C, Zero) Name (R420, Zero) Name (R424, Zero) Name (R428, Zero) Name (R42C, Zero) Name (RVES, Zero) Name (R518, Zero) Name (R519, Zero) Name (R51A, Zero) Name (R51C, Zero) Name (R520, Zero) Name (R524, Zero) Name (R528, Zero) Name (R52C, Zero) Name (R618, Zero) Name (R619, Zero) Name (R61A, Zero) Name (R61C, Zero) Name (R620, Zero) Name (R624, Zero) Name (R628, Zero) Name (R62C, Zero) Name (RH10, Zero) Name (RH14, Zero) Name (POC0, Zero) OperationRegion (RSTR, SystemMemory, NHI1, 0x0100) Field (RSTR, DWordAcc, NoLock, Preserve) { CIOR, 32, Offset (0xB8), ISTA, 32, Offset (0xF0), ICME, 32 } OperationRegion (T2PM, SystemMemory, T2P1, 0x08) Field (T2PM, DWordAcc, NoLock, Preserve) { T2PR, 32, P2TR, 32 } OperationRegion (RPSM, SystemMemory, 0x60510000, 0x54) Field (RPSM, DWordAcc, NoLock, Preserve) { RPVD, 32, RPR4, 8, Offset (0x18), RP18, 8, RP19, 8, RP1A, 8, Offset (0x1C), RP1C, 16, Offset (0x20), R_20, 32, R_24, 32, R_28, 32, R_2C, 32, Offset (0x52), , 11, RPLT, 1, Offset (0x54) } OperationRegion (UPSM, SystemMemory, TUP1, 0x0548) Field (UPSM, DWordAcc, NoLock, Preserve) { UPVD, 32, UP04, 8, Offset (0x08), CLRD, 32, Offset (0x18), UP18, 8, UP19, 8, UP1A, 8, Offset (0x1C), UP1C, 16, Offset (0x20), UP20, 32, UP24, 32, UP28, 32, UP2C, 32, Offset (0xD2), , 11, UPLT, 1, Offset (0xD4), Offset (0x544), UPMB, 1, Offset (0x548) } OperationRegion (DNSM, SystemMemory, TDB1, 0xD4) Field (DNSM, DWordAcc, NoLock, Preserve) { DPVD, 32, DP04, 8, Offset (0x18), DP18, 8, DP19, 8, DP1A, 8, Offset (0x1C), DP1C, 16, Offset (0x20), DP20, 32, DP24, 32, DP28, 32, DP2C, 32, Offset (0xD2), , 11, DPLT, 1, Offset (0xD4) } OperationRegion (DS3M, SystemMemory, TD11, 0x40) Field (DS3M, DWordAcc, NoLock, Preserve) { D3VD, 32, D304, 8, Offset (0x18), D318, 8, D319, 8, D31A, 8, Offset (0x1C), D31C, 16, Offset (0x20), D320, 32, D324, 32, D328, 32, D32C, 32 } OperationRegion (DS4M, SystemMemory, TD21, 0x0568) Field (DS4M, DWordAcc, NoLock, Preserve) { D4VD, 32, D404, 8, Offset (0x18), D418, 8, D419, 8, D41A, 8, Offset (0x1C), D41C, 16, Offset (0x20), D420, 32, D424, 32, D428, 32, D42C, 32, Offset (0x564), DVES, 32 } OperationRegion (DS5M, SystemMemory, TD41, 0x40) Field (DS5M, DWordAcc, NoLock, Preserve) { D5VD, 32, D504, 8, Offset (0x18), D518, 8, D519, 8, D51A, 8, Offset (0x1C), D51C, 16, Offset (0x20), D520, 32, D524, 32, D528, 32, D52C, 32 } OperationRegion (NHIM, SystemMemory, TNH1, 0x40) Field (NHIM, DWordAcc, NoLock, Preserve) { NH00, 32, NH04, 8, Offset (0x10), NH10, 32, NH14, 32 } Method (_INI, 0, NotSerialized) // _INI: Initialize { If (LNot (OSDW ())) { Store (One, TBG2) Store (R_20, R020) Store (R_24, R024) Store (R_28, R028) Store (R_2C, R02C) Store (UP18, R118) Store (UP19, R119) Store (UP1A, R11A) Store (UP1C, R11C) Store (UP20, R120) Store (UP24, R124) Store (UP28, R128) Store (UP2C, R12C) Store (DP18, R218) Store (DP19, R219) Store (DP1A, R21A) Store (DP1C, R21C) Store (DP20, R220) Store (DP24, R224) Store (DP28, R228) Store (DP28, R228) Store (D318, R318) Store (D319, R319) Store (D31A, R31A) Store (D31C, R31C) Store (D320, R320) Store (D324, R324) Store (D328, R328) Store (D32C, R32C) Store (D418, R418) Store (D419, R419) Store (D41A, R41A) Store (D41C, R41C) Store (D420, R420) Store (D424, R424) Store (D428, R428) Store (D42C, R42C) Store (DVES, RVES) Store (D518, R518) Store (D519, R519) Store (D51A, R51A) Store (D51C, R51C) Store (D520, R520) Store (D524, R524) Store (D528, R528) Store (D52C, R52C) Store (NH10, RH10) Store (NH14, RH14) Sleep (One) ICMB () } } etc. etc. anyway fail on our Hackintosh systems.. Noticeable, that in the actual DSDT.aml, UPSB is also part of the the_GPE implementation. The remaining TB DSDT patches seem to consist of a simple DSB0 and DSB2 "PCIHotplugCapable" property injection and the usual ACPI TB device definitions. In my opinion, nothing that could result in the TB miracle observed above..1 point

-

I guess he implemented it in his post? See his Send me Paulos-Mac-Pro.zip... But there is nothing than a DSDT.aml in EFI/CLOVER/ACPI/patched/..1 point

-

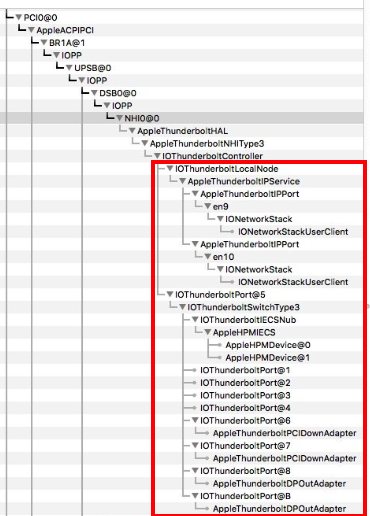

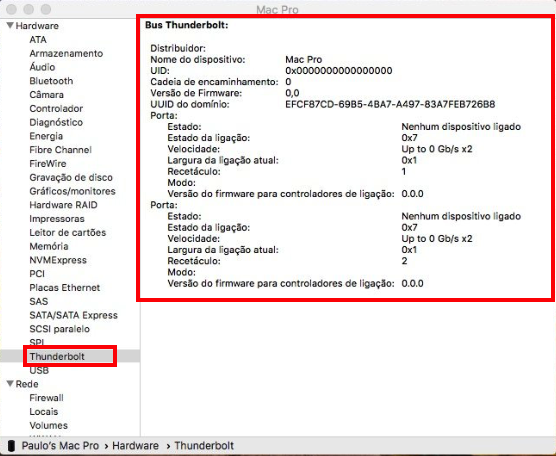

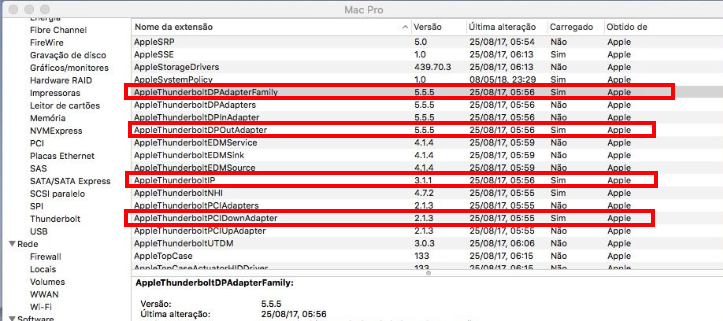

Looks rather like a miracle... or to say it in simple words... you are the one out of millions not affected by the virus... and nobody knows why.. My goodness... you have a fully implemented local thunderbolt node and even the thunderbolt bus driver loaded While usually in TB Hackintosh systems only the IOThunderboltFamily.kext and ThunderboltNHI.kext are active, you also have the AppleThunderboltDPAdapaterFamily.kext, the AppleThunderboltDPOutAdapter.kext, the AppleThunderboltIP.kext the AppleThunderboltPCIDownAdapter.kext active on your system.. Some TB kexts not marked in red are still missing though also on your system.. Anyway.. no idea how all this is possible without doing anything else then configuring the TB BIOS settings like we all did? You do not even mention a SSDT, although I do not understand how you obtain without the latter the UPSB, DSB0, DSB1, DSB2, DSB4, NHI0 and XHC2 ACPI implementation..1 point

-

AppleHDA patching is probably one of the most complex and in depth processes one can choose to learn in the Hackingtosh world, I only understand a very small part of it namely setting the pin config data. Even with well written guides it's still very complex if your new to it, there are a few AppleHDA patching masters and guru's in this area and if you need more specific help I suggest sending a PM to one of them. The most complete guide i know of is the one written by EMlyDinEsH here :- https://osxlatitude.com/forums/topic/1946-complete-applehda-patching-guide/ Its old but still very valid as nothing has really changed in the process and although it's written as a AppleHDA patching guide everything in there is relevant to AppleALC, put rather simply AppleALC is basically a AppleHDA patching engine, with an internal database of patches, layout and platforms files for all the codecs that it supports. If you create a new layout then you simply need to add it to the relevant codec folder in the AppleALC source and add a few lines to the relevant info.plist which defines the new layout's id, platform and layout files to use. Some information on this is in the AppleALC wiki. If you just need to collect and set the pin config data then this guide by MacPeet may be a better option :- https://www.root86.com/blog/40/entry-51-guide-anleitung-patch-applehda/ (it's in German but if you use chrome it will automatically translate it for you) Cheers Jay1 point

-

I apologize friends, but this discussion of what drivers are needed for this or that, has already made me delete some, come back again and I do not use FV2. Why not separate into the Clover installation options? Type: "UEFI Drivers without FV2" and "UEFI Drivers with FV2" Thanks1 point

-

1 point

-

You used the latest one here, https://github.com/Shaneee92/AMD-High-Sierra-XNU/releases It's confirmed working on FX. 10.13.5 though you need to roll back alot of kexts to get the prelinkedkernel to compile.1 point

-

1 point

-

on gigabyte maybe working, but on asus mainboard not ... you both have gigabyte mobo ...0 points