All Activity

- Past hour

-

Gacor Aladin changed their profile photo

-

Marketing Profit Media changed their profile photo

-

Döner boey changed their profile photo

-

@sergANt Welcome! I hope that the thread about Intel 11th gen GPUs could be useful for you and others.

- 5,227 replies

-

- hello

- insanelymac

-

(and 2 more)

Tagged with:

-

this is still very bugged. goal is extract kexts and make it load in ghidra for debug purposes ment to use with BootKernelExtensions.kc or syskernel not for extract from cache load it in xcode so you can check what its doing i have set in main() the file loading

- Today

-

Dynasty Gameplay changed their profile photo

-

Best Restaurants In Regina changed their profile photo

-

23lk Coocxe changed their profile photo

-

Caustin Mclaughlin changed their profile photo

-

Hello everyone. My name is Sergio. Starting from the socket-1366 platform, I've been installing macOS on PC. Today, I have a laptop based on the i7-11800h processor, and I'm experiencing issues with the iGPU. I found a wonderful topic on this forum about graphics on Intel 11th gen processors. I hope we can work together to get the Intel iGPU 11th gen up and running. Thanks!

- 5,227 replies

-

- 1

-

-

- hello

- insanelymac

-

(and 2 more)

Tagged with:

-

zindo joined the community

-

miliuco started following OCLP and sip disabled

-

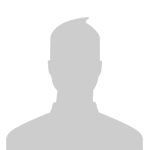

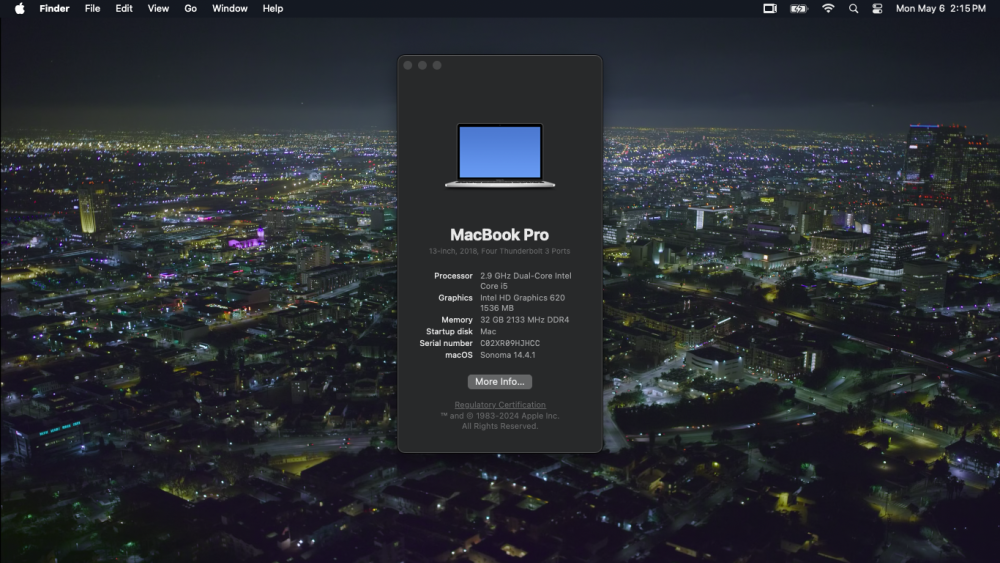

@bluenote56 Set this 2 keys as in the pic, csr-active-config is 03080000 as @ichelash says. But, if it doesn't exist, add csr-active-config in NVRAM -> Delete ->7C436110-AB2A-4BBB-A880-FE41995C9F82. ResetNVRAM at first boot after the change.

-

Solnukua joined the community

-

Talha Jutt changed their profile photo

-

dimedia nuovimo joined the community

-

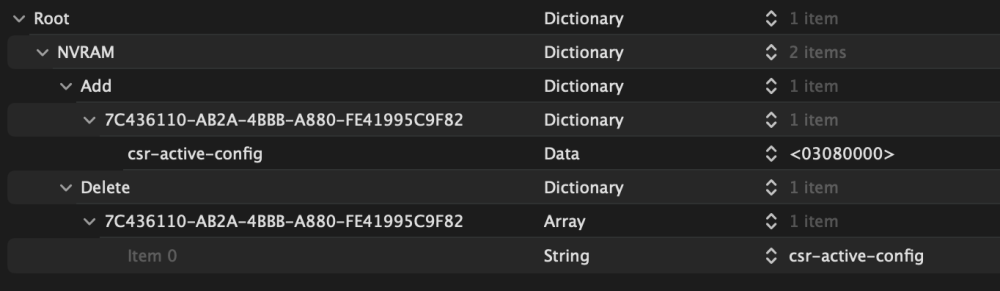

See, required 0x802 while you set 0x26f. There are different digits. Look carefully your opencore config.plist

-

Dmitriy Karpovich joined the community

-

Hi I tried changing csr value but there must be something wrong in what I do.. maybe my OC EFI, it's impossible that csrutil status shows disabled and OCLP always gives the same result..

-

neha smartparts changed their profile photo

-

whateveritisthatitis joined the community

-

Hellstar joined the community

-

now the undefined8 AppleIntelFramebufferController::hwEnableInterrupts(void) as this defs + some i can't find in recent linux sources this are the defs for both #define GEN11_GFX_MSTR_IRQ (0x190010) #define SOUTH_CHICKEN1 (0xc2000) #define GEN8_MASTER_IRQ (0x44200) #define PCH_PORT_HOTPLUG (0xc4030) #define SHOTPLUG_CTL_DDI (0xc4030) #define SHOTPLUG_CTL_TC (0xc4034) #define SHPD_FILTER_CNT (0xc4038) #define SDEIMR (0xc4004) #define SDEIIR (0xc4008) #define SDEIER (0xc400c) #define GEN11_DE_HPD_ISR (0x44470) #define GEN11_DE_HPD_IMR (0x44474) #define GEN11_DE_HPD_IIR (0x44478) #define GEN11_DE_HPD_IER (0x4447c) #define GEN8_DE_MISC_ISR (0x44460) #define GEN8_DE_MISC_IMR (0x44464) #define GEN8_DE_MISC_IIR (0x44468) #define GEN8_DE_MISC_IER (0x4446c) #define GEN8_DE_PIPE_ISR_A (0x44400) #define GEN8_DE_PIPE_IMR_A (0x44404) #define GEN8_DE_PIPE_IIR_A (0x44408) #define GEN8_DE_PIPE_IER_A (0x4440c) #define GEN8_DE_PIPE_ISR_B (0x44410) #define GEN8_DE_PIPE_IMR_B (0x44414) #define GEN8_DE_PIPE_IIR_B (0x44418) #define GEN8_DE_PIPE_IER_B (0x4441c) #define GEN8_DE_PIPE_ISR_C (0x44420) #define GEN8_DE_PIPE_IMR_C (0x44424) #define GEN8_DE_PIPE_IIR_C (0x44428) #define GEN8_DE_PIPE_IER_C (0x4442c) WriteRegister32(in_RDI,0x190010,0x80000000); = static inline void gen11_master_intr_enable(void __iomem * const regs) { raw_reg_write(regs, GEN11_GFX_MSTR_IRQ, GEN11_MASTER_IRQ); } this function is in apple code undefined8 AppleIntelFramebufferController::ProcessInterrupt(void) void gen11_display_irq_handler(struct drm_i915_private *i915) { void __iomem * const regs = intel_uncore_regs(&i915->uncore); const u32 disp_ctl = raw_reg_read(regs, GEN11_DISPLAY_INT_CTL); disable_rpm_wakeref_asserts(&i915->runtime_pm); /* * GEN11_DISPLAY_INT_CTL has same format as GEN8_MASTER_IRQ * for the display related bits. */ raw_reg_write(regs, GEN11_DISPLAY_INT_CTL, 0x0); gen8_de_irq_handler(i915, disp_ctl); raw_reg_write(regs, GEN11_DISPLAY_INT_CTL, GEN11_DISPLAY_IRQ_ENABLE); enable_rpm_wakeref_asserts(&i915->runtime_pm); } dam irqs https://elixir.bootlin.com/linux/latest/source/drivers/gpu/drm/i915/gt/intel_gt_irq.c

- 167 replies

-

- whatevergreen

- iris xe

-

(and 1 more)

Tagged with:

-

-

Gracek changed their profile photo

-

Mahmudul Kabir joined the community

-

Kevin Stratos joined the community

-

Chris Floyd joined the community

-

HP EliteDesk 800 G4 Mini with RX560 dGPU

CloverLeaf replied to deeveedee's topic in Installation Guides

@deeveedee Yes, I saw that but it didn't fix the issue for me. I will test again in a few days. -

HP EliteDesk 800 G4 Mini with RX560 dGPU

deeveedee replied to deeveedee's topic in Installation Guides

@CloverLeaf Pastrychef's black screen was fixed by eliminating WhateverGreen.kext. I plan to find a solution that keeps WEG. I'll be able to start looking at this later this week. -

I don't know how Windows lives. Once I tested 3D graphics in Windows with two cases HPET switched on in BIOS and off. The results are different but Windows works in both cases.

-

@Slice - @MaLd0n 's Proposed config.plist includes unconditional ACPI patches that change TMR, RTC and PIC IRQs. My question remains - if not obsolete, why don't these changes affect Windows? I'm asking because I don't know - not because I'm challenging anyone.

-

-

-

why no ioreg or logs ? without them we can't help there's no such code in icl gen11 int... static irq_handler_t intel_irq_handler(struct drm_i915_private *dev_priv) { if (HAS_GMCH(dev_priv)) { if (IS_CHERRYVIEW(dev_priv)) return cherryview_irq_handler; else if (IS_VALLEYVIEW(dev_priv)) return valleyview_irq_handler; else if (GRAPHICS_VER(dev_priv) == 4) return i965_irq_handler; else if (GRAPHICS_VER(dev_priv) == 3) return i915_irq_handler; else return i8xx_irq_handler; } else { if (GRAPHICS_VER_FULL(dev_priv) >= IP_VER(12, 10)) return dg1_irq_handler; else if (GRAPHICS_VER(dev_priv) >= 11) return gen11_irq_handler; else if (GRAPHICS_VER(dev_priv) >= 😎 return gen8_irq_handler; else return ilk_irq_handler; } } if icl is gen8 then static inline void gen8_master_intr_enable(void __iomem * const regs) { raw_reg_write(regs, GEN8_MASTER_IRQ, GEN8_MASTER_IRQ_CONTROL); } and we need static inline void gen11_master_intr_enable(void __iomem * const regs) { raw_reg_write(regs, GEN11_GFX_MSTR_IRQ, GEN11_MASTER_IRQ); } confirmed icl frame uses GEN8_MASTER_IRQ a lot in apple code undefined8 AppleIntelFramebufferController::hwDisableInterrupts(void) { uint uVar1; AppleIntelFramebufferController *in_RDI; _DAT_0010dd28 = _DAT_0010dd28 + 1; interruptLock(); if ((in_RDI->m_AppleIntelFramebufferController).field_0xfcc != '\0') { _DAT_0010dd30 = _DAT_0010dd30 + 1; (in_RDI->m_AppleIntelFramebufferController).field_0xfcc = 0; WriteRegister32(in_RDI,0x44200,0); DAT_0010d338 = DAT_0010d338 + 1; uVar1 = ReadRegister32(in_RDI,0xc2000); WriteRegister32(in_RDI,0xc2000,uVar1 | 0x80); WriteRegister32(in_RDI,0xc4004,0xffffffff); WriteRegister32(in_RDI,0xc400c,0); WriteRegister32(in_RDI,0xc4008,0xffffffff); WriteRegister32(in_RDI,0xc4008,0xffffffff); uVar1 = ReadRegister32(in_RDI,0xc2000); WriteRegister32(in_RDI,0xc2000,uVar1 & 0xffffff7f); WriteRegister32(in_RDI,0x44474,0xffffffff); WriteRegister32(in_RDI,0x4447c,0); WriteRegister32(in_RDI,0x44478,0xffffffff); WriteRegister32(in_RDI,0x44478,0xffffffff); WriteRegister32(in_RDI,0x44464,0xffffffff); WriteRegister32(in_RDI,0x4446c,0); WriteRegister32(in_RDI,0x44468,0xffffffff); WriteRegister32(in_RDI,0x44468,0xffffffff); WriteRegister32(in_RDI,0x44404,0xffffffff); WriteRegister32(in_RDI,0x4440c,0); WriteRegister32(in_RDI,0x44408,0xffffffff); WriteRegister32(in_RDI,0x44408,0xffffffff); WriteRegister32(in_RDI,0x44414,0xffffffff); WriteRegister32(in_RDI,0x4441c,0); WriteRegister32(in_RDI,0x44418,0xffffffff); WriteRegister32(in_RDI,0x44418,0xffffffff); WriteRegister32(in_RDI,0x44424,0xffffffff); WriteRegister32(in_RDI,0x4442c,0); WriteRegister32(in_RDI,0x44428,0xffffffff); WriteRegister32(in_RDI,0x44428,0xffffffff); } interruptUnlock(); return 0; } so... #define SOUTH_CHICKEN1 (0xc2000) #define GEN8_MASTER_IRQ (0x44200) #define SDEIMR (0xc4004) #define SDEIIR (0xc4008) #define SDEIER (0xc400c) #define GEN11_DE_HPD_ISR (0x44470) #define GEN11_DE_HPD_IMR (0x44474) #define GEN11_DE_HPD_IIR (0x44478) #define GEN11_DE_HPD_IER (0x4447c) #define GEN8_DE_MISC_ISR (0x44460) #define GEN8_DE_MISC_IMR (0x44464) #define GEN8_DE_MISC_IIR (0x44468) #define GEN8_DE_MISC_IER (0x4446c) #define GEN8_DE_PIPE_ISR_A (0x44400) #define GEN8_DE_PIPE_IMR_A (0x44404) #define GEN8_DE_PIPE_IIR_A (0x44408) #define GEN8_DE_PIPE_IER_A (0x4440c) #define GEN8_DE_PIPE_ISR_B (0x44410) #define GEN8_DE_PIPE_IMR_B (0x44414) #define GEN8_DE_PIPE_IIR_B (0x44418) #define GEN8_DE_PIPE_IER_B (0x4441c) #define GEN8_DE_PIPE_ISR_C (0x44420) #define GEN8_DE_PIPE_IMR_C (0x44424) #define GEN8_DE_PIPE_IIR_C (0x44428) #define GEN8_DE_PIPE_IER_C (0x4442c) and them undefined8 AppleIntelFramebufferController::hwDisableInterrupts(void) { uint regValue; AppleIntelFramebufferController *thisPointer; interruptCounter = interruptCounter + 1; interruptLock(); if (thisPointer->interruptEnabledFlag != '\0') { disableInterruptCounter = disableInterruptCounter + 1; thisPointer->interruptEnabledFlag = 0; WriteRegister32(thisPointer, GEN8_MASTER_IRQ, 0); miscInterruptCounter = miscInterruptCounter + 1; regValue = ReadRegister32(thisPointer, SOUTH_CHICKEN1); WriteRegister32(thisPointer, SOUTH_CHICKEN1, regValue | 0x80); WriteRegister32(thisPointer, SDEIMR, 0xffffffff); WriteRegister32(thisPointer, SDEIER, 0); WriteRegister32(thisPointer, SDEIIR, 0xffffffff); WriteRegister32(thisPointer, SDEIIR, 0xffffffff); regValue = ReadRegister32(thisPointer, SOUTH_CHICKEN1); WriteRegister32(thisPointer, SOUTH_CHICKEN1, regValue & 0xffffff7f); WriteRegister32(thisPointer, GEN11_DE_HPD_IMR, 0xffffffff); WriteRegister32(thisPointer, GEN11_DE_HPD_IER, 0); WriteRegister32(thisPointer, GEN11_DE_HPD_IIR, 0xffffffff); WriteRegister32(thisPointer, GEN11_DE_HPD_IIR, 0xffffffff); WriteRegister32(thisPointer, GEN8_DE_MISC_IMR, 0xffffffff); WriteRegister32(thisPointer, GEN8_DE_MISC_IER, 0); WriteRegister32(thisPointer, GEN8_DE_MISC_IIR, 0xffffffff); WriteRegister32(thisPointer, GEN8_DE_MISC_IIR, 0xffffffff); WriteRegister32(thisPointer, GEN8_DE_PIPE_IMR_A, 0xffffffff); WriteRegister32(thisPointer, GEN8_DE_PIPE_IER_A, 0); WriteRegister32(thisPointer, GEN8_DE_PIPE_IIR_A, 0xffffffff); WriteRegister32(thisPointer, GEN8_DE_PIPE_IIR_A, 0xffffffff); WriteRegister32(thisPointer, GEN8_DE_PIPE_IMR_B, 0xffffffff); WriteRegister32(thisPointer, GEN8_DE_PIPE_IER_B, 0); WriteRegister32(thisPointer, GEN8_DE_PIPE_IIR_B, 0xffffffff); WriteRegister32(thisPointer, GEN8_DE_PIPE_IIR_B, 0xffffffff); WriteRegister32(thisPointer, GEN8_DE_PIPE_IMR_C, 0xffffffff); WriteRegister32(thisPointer, GEN8_DE_PIPE_IER_C, 0); WriteRegister32(thisPointer, GEN8_DE_PIPE_IIR_C, 0xffffffff); WriteRegister32(thisPointer, GEN8_DE_PIPE_IIR_C, 0xffffffff); } interruptUnlock(); return 0; }

- 167 replies

-

- 1

-

-

- whatevergreen

- iris xe

-

(and 1 more)

Tagged with:

-

I said nothing about RTC and PIC. They are not obsolete.

-

I am not sure but may be you may activate VESA mode somehow. For example by faking device-id to comet lake value.

-

Yes, I do.

-

HP EliteDesk 800 G4 Mini with RX560 dGPU

CloverLeaf replied to deeveedee's topic in Installation Guides

Nice! Last time I tried playing with RX560 I was not able to pass the black screen after boot. @pastrychef had exactly the same issue. Seems like everything is working but no video output. I would love to see your Mini working! PS: Just ordered Mini G4+RX560.... Will contribute to the troubleshooting soon. -

I can't get past the ACPI errors even with setting ig-platform-id to 12345678. Also, do you mean the graphics will never be able to be activated in the future?

-

@Slice So the only reason that the TMR, RTC and PIC IRQ ACPI patches don't affect Windows is because they are unnecessary? As I mentioned, I stopped applying IRQ patches after I started disabling HPET (which Apple did, I think starting with Mac Models in 2018).

-

michalama started following Post installation problems..

-

dwgraham172 started following Eng Mohamed Salah

-

dwgraham172 started following sergANt

-

dwgraham172 started following Anto65

-

dwgraham172 started following ontimemovingdelivery

-

dwgraham172 started following Multitech Elevators

-

dwgraham172 started following Mr.Enrich

-

dwgraham172 started following Brianna Schoonewolff

-

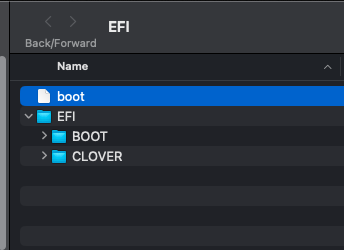

@Slice We need to Write MBR ; See Script Clover_Duet Anyone want to use Clover-LegacyDuet # Clone the repository git clone https://github.com/CloverHackyColor/Clover-LegacyDuet.git # Put your Clover (EFI folder) on Clover-LegacyDuet repository # Run Clover_Duet.command Result You don't know how to use Clover Duet 🚫 Do not use this program on a disk where Clover or OpenCore is already installed!

- 29,867 replies

-

- 2

-

-

- bootloader

- efi

-

(and 2 more)

Tagged with:

-

so I've tried copying HP-EliteBook-840-G4>Packages>OC-EFI>EFI over to my EFI and when booting it never gets passed all the coding. I've tried making OC from HP-EliteBook-840-G4>Create_App.command and when booting it never gets passed all the coding. I've tried making OC from HP-EliteBook-840-G4>Packages>OC-Package and when booting it never gets passed all the coding. I can only boot from my original EFI folder that was successful making Big Sur. and when I install OCLP I can’t even make it to the Apple logo. Last edit. For whatever reason resetting the ram breaks the installer. All I had to do to my old EFI folder was get the 2 kext for Broadcom wifi and put those in my kext folder change some things in OpenCore config and presto. Reached the promise land.

-

The EFI for Open Core is still experimental, having some issues with USB mounting, DVD Drive etc. Keep in mind, I changed the EDID for the AOU FullHD Screen mod. If you use stock screen, use the stock EDID in Tlucks package. Bear in mind I'm using an i7-2720QM CPU so maybe CpuPM is not working properly. EFI T420 V1 Tluck.zip