Leaderboard

Popular Content

Showing content with the highest reputation on 02/05/2020 in all areas

-

4 points

-

I have to remind that legacy boot have stages: 1. BIOS jumps to a small program written into boot0 sector from MBR block 0 on a device. 2. boot0 program searches a bootable partition containing boot1 program in the first block. Jump to boot1. 3. boot1 searches for file boot on the partition. So it must know file system on the partition. Because of that we have three kind of boot1 boot1f32 for FAT32 partition boot1h for HFS+ partition boot1x for exFAT partition And I see AnV written boot1n for NTFS partition. That's all. We have no boot1 for APFS, EXT2/4 etc. As well boot1f32 will not work on FAT16 because for slightly different offsets of FAT table and different signature. I may propose that good programmer is able to write boot1f16 but I see no such file yet.3 points

-

I compiled an hybrid 32 and 64 bits executable which works as expected on catalina and mountain lion on a 64 bit machine, if you are running a 32 bit machine or a 32 bit installation of mac os x and you want to test the driver pm me2 points

-

I means how to change default background and selector or maybe it's a concept GUI2 points

-

Good catch, Thanks, ya it would create assert error if Oc Version wasn't allowed to show, it's fixed now.2 points

-

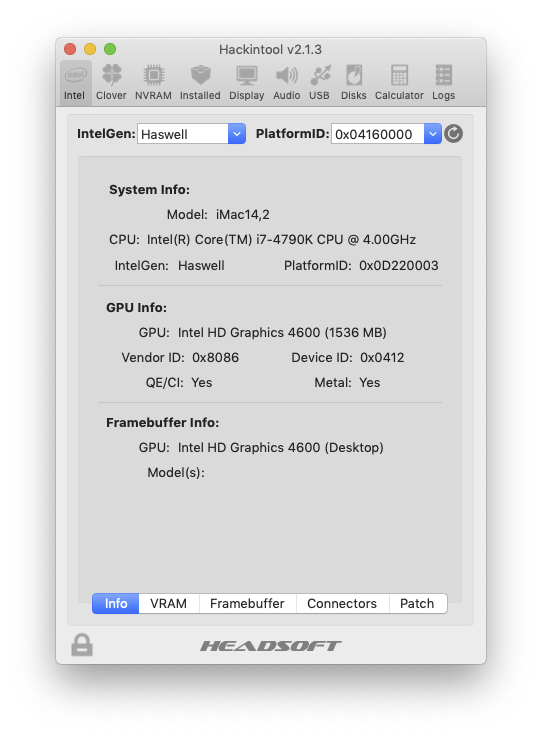

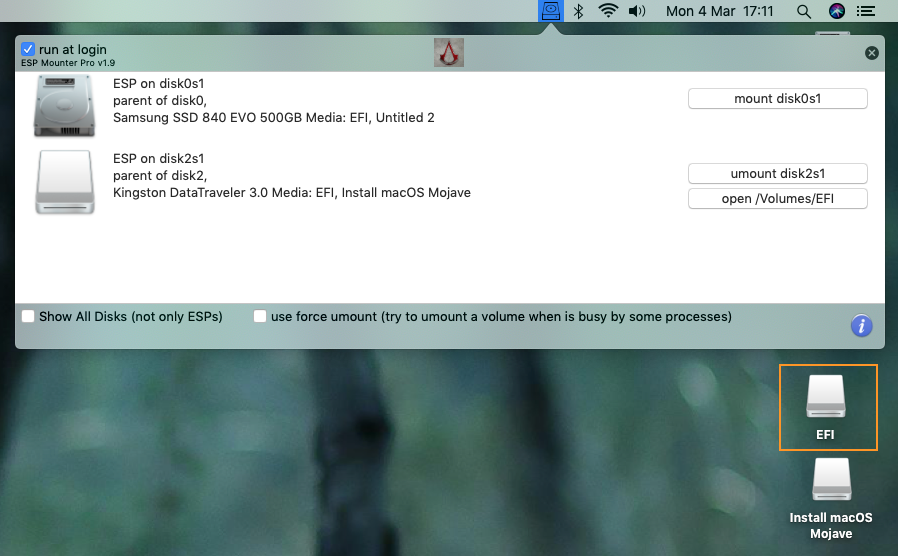

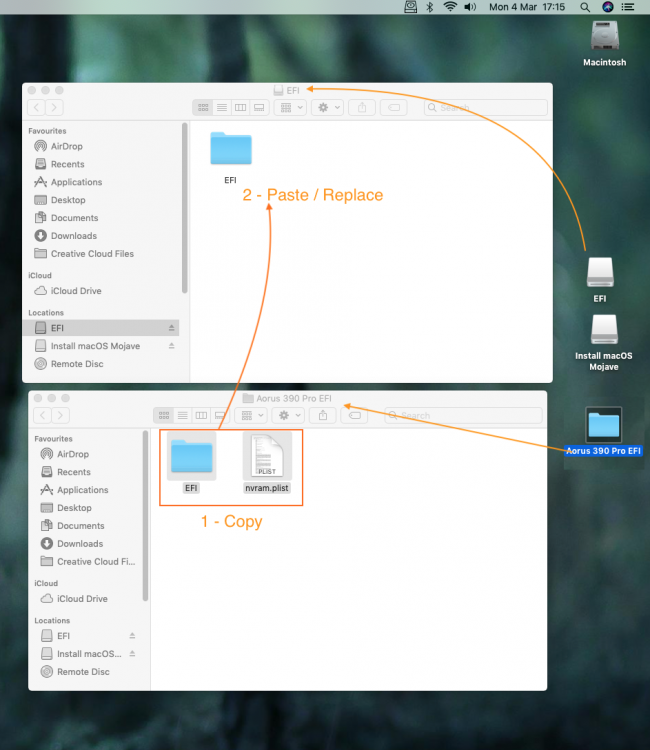

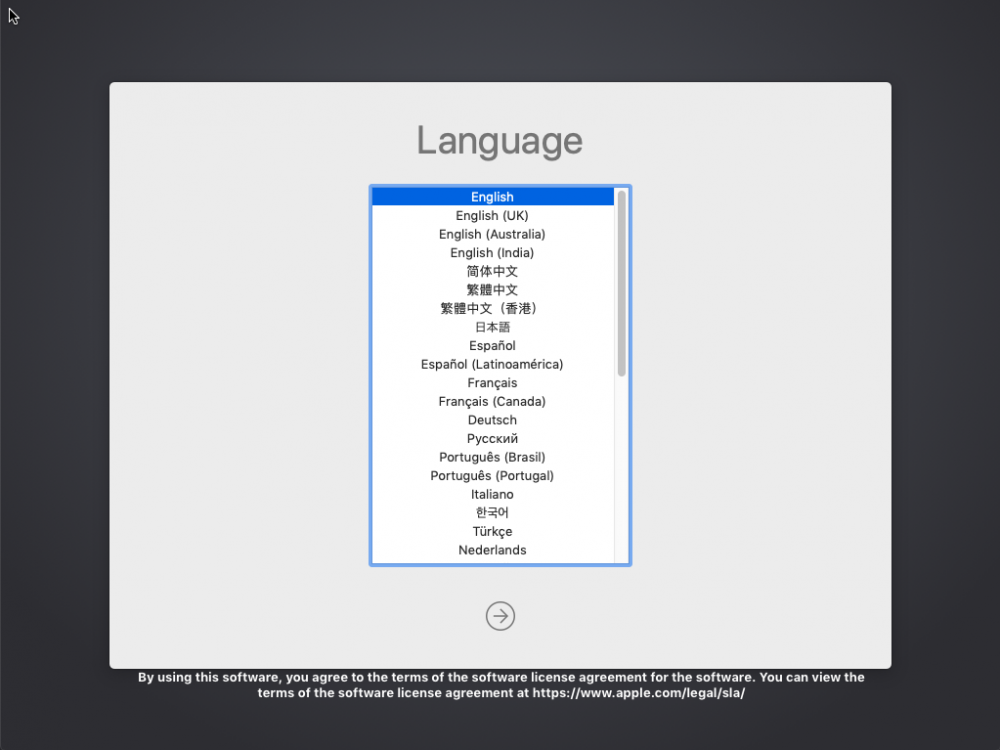

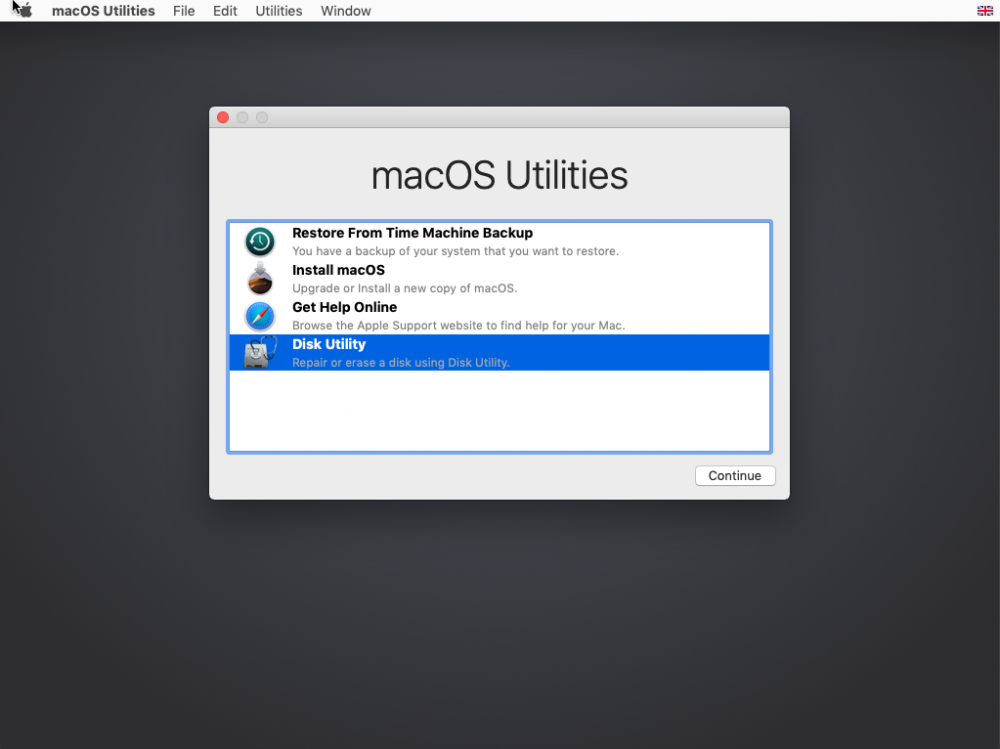

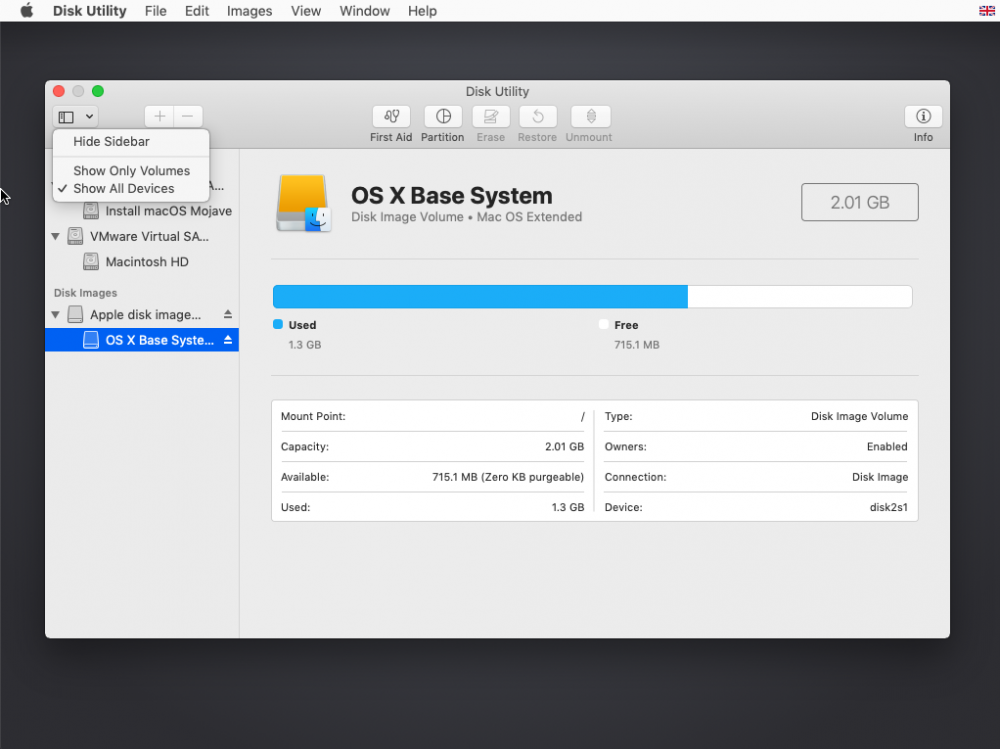

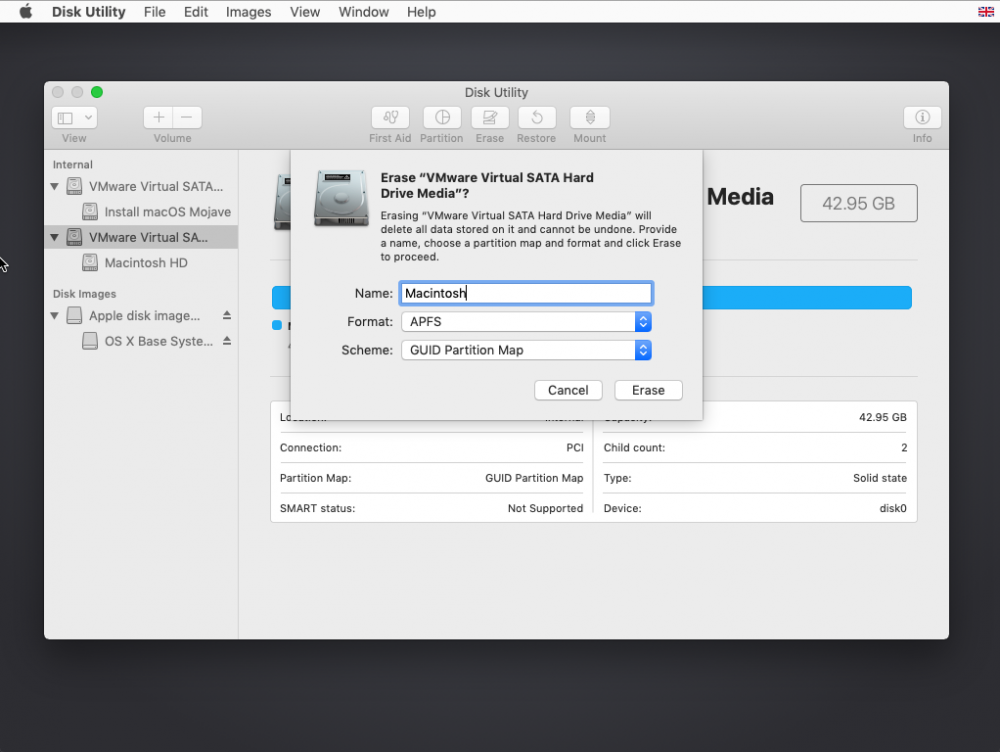

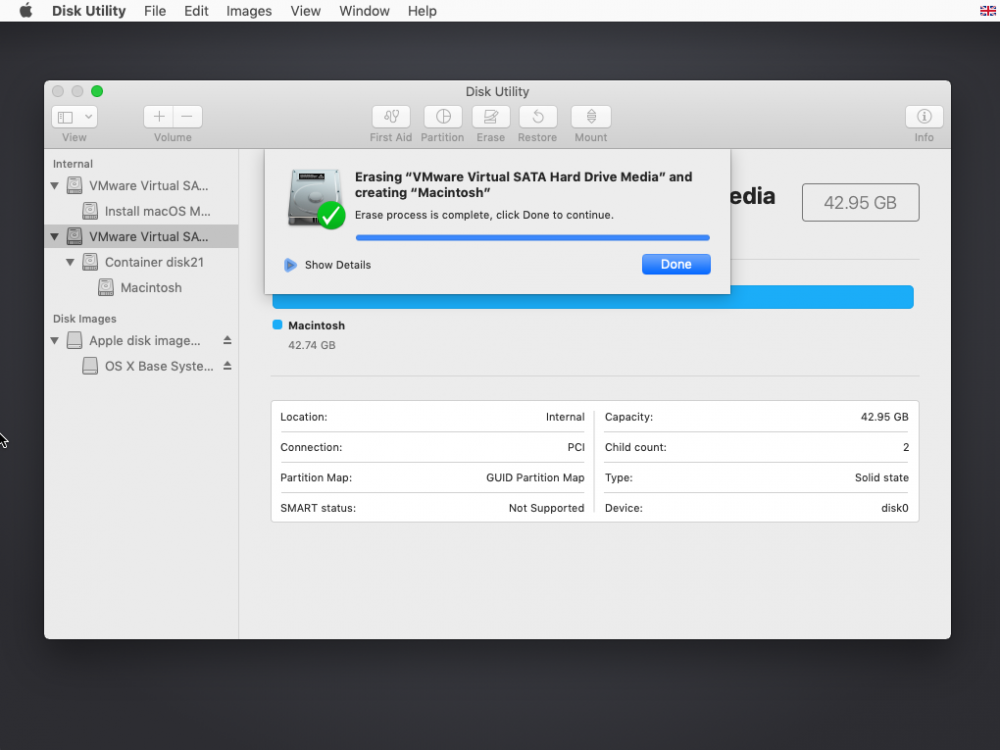

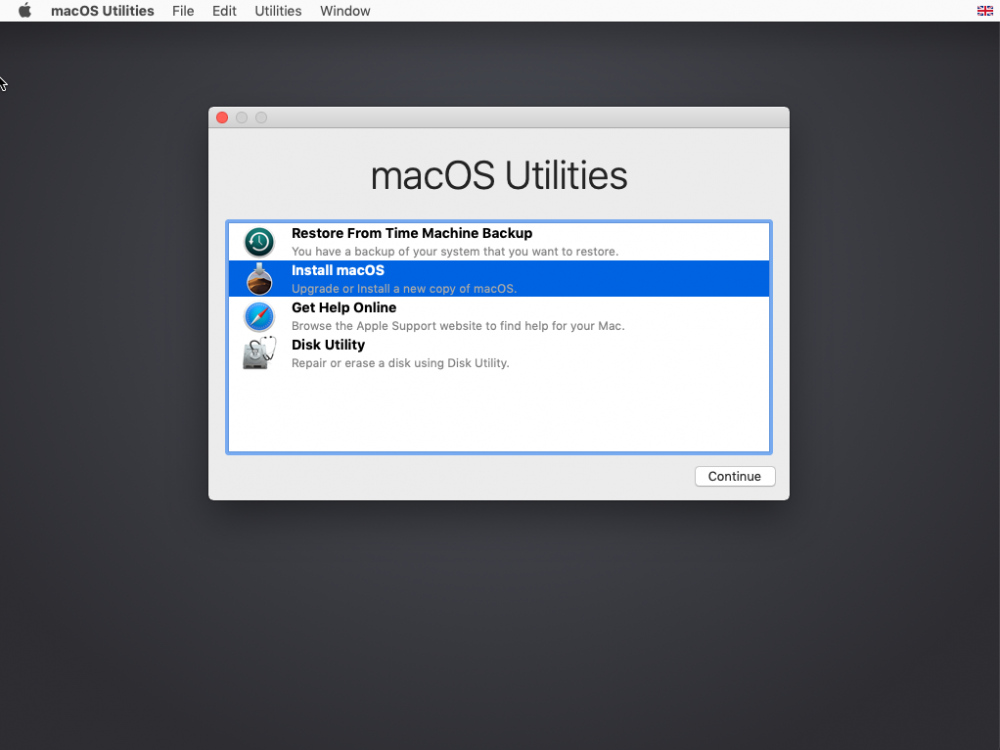

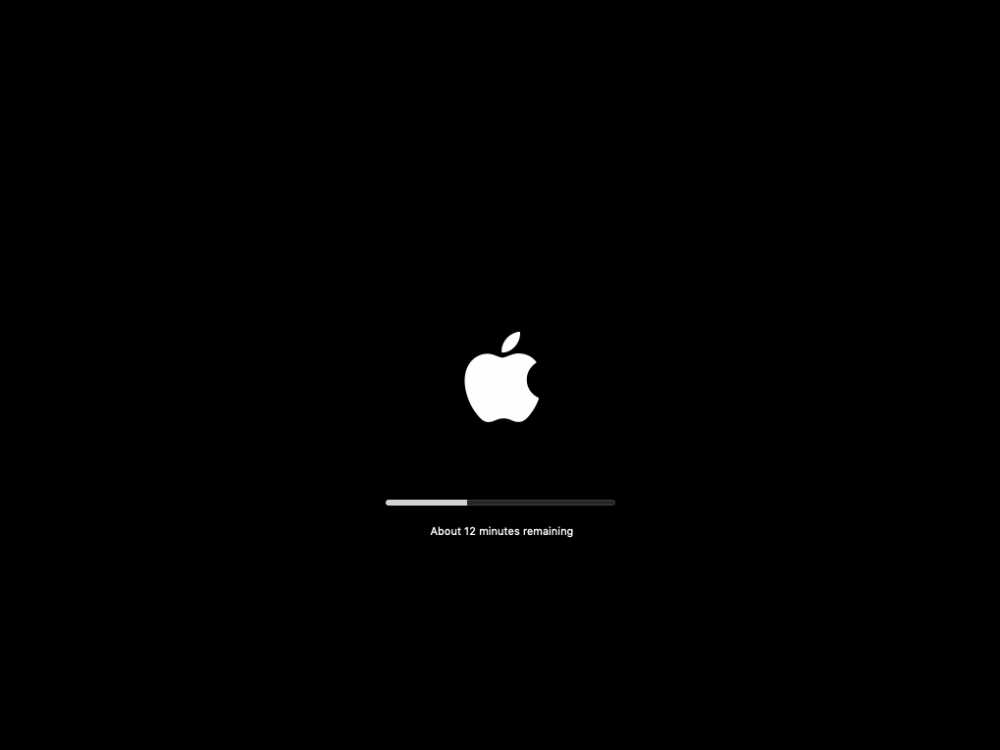

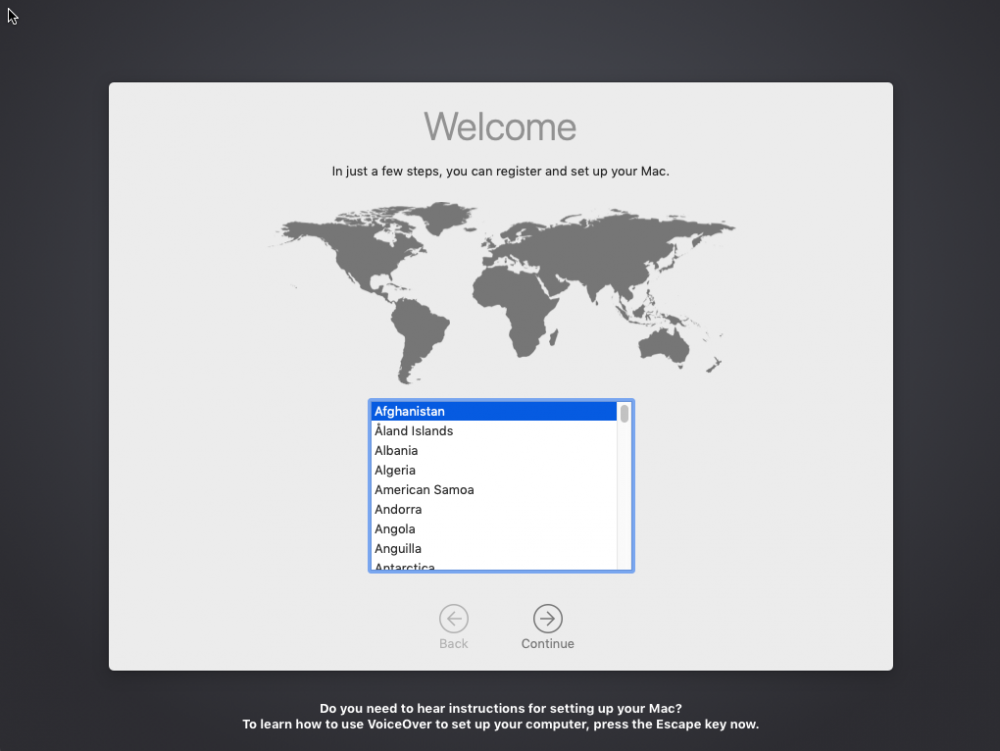

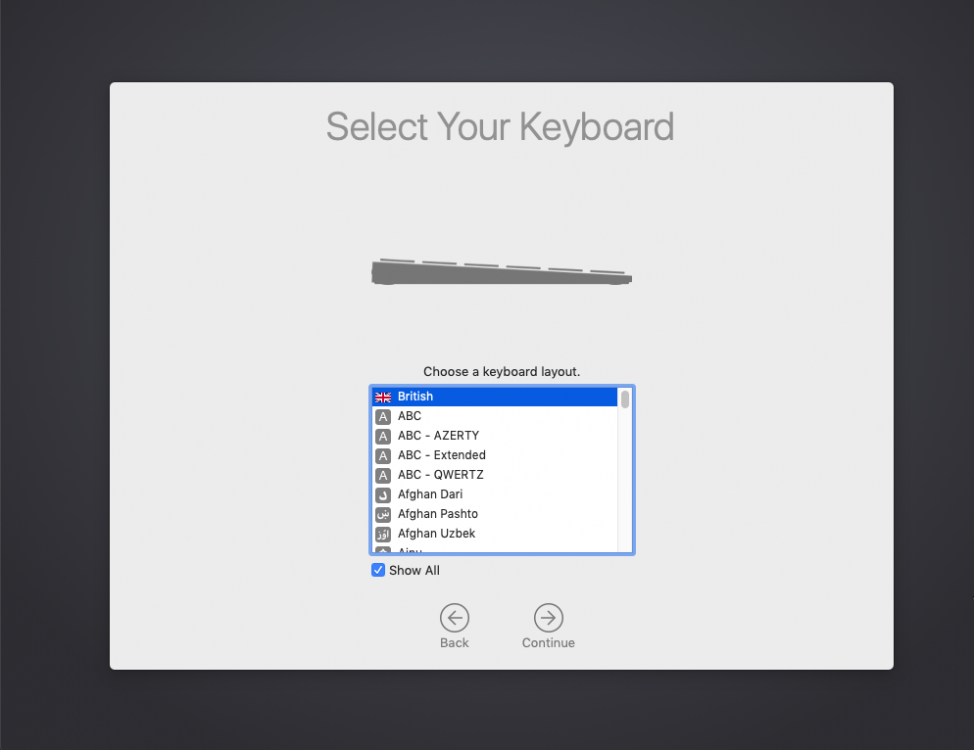

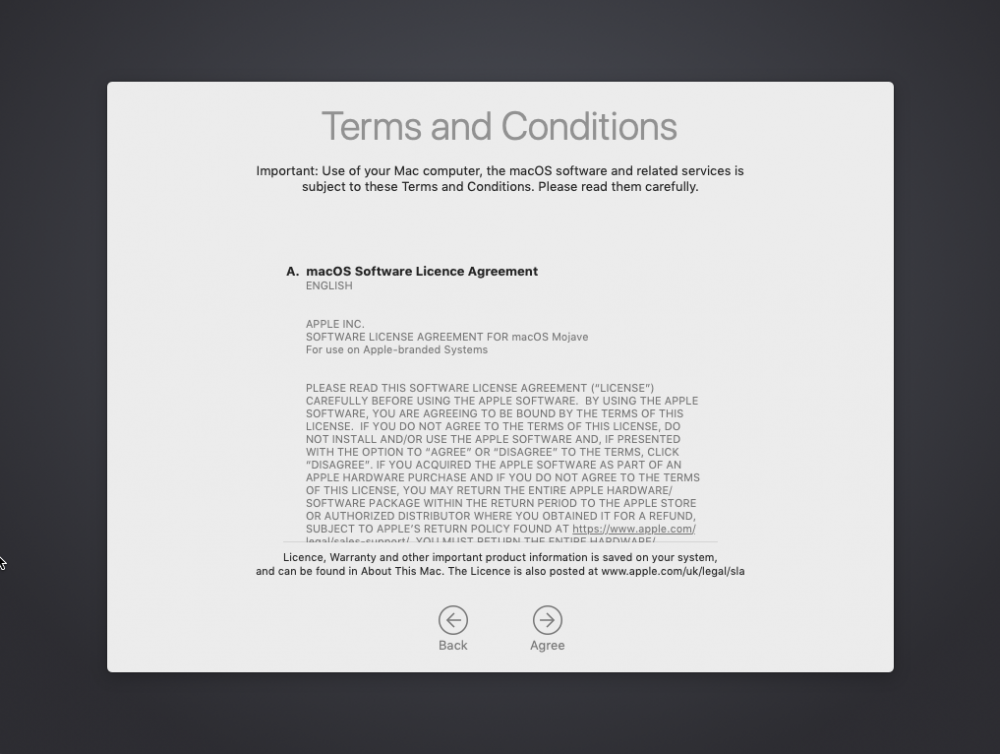

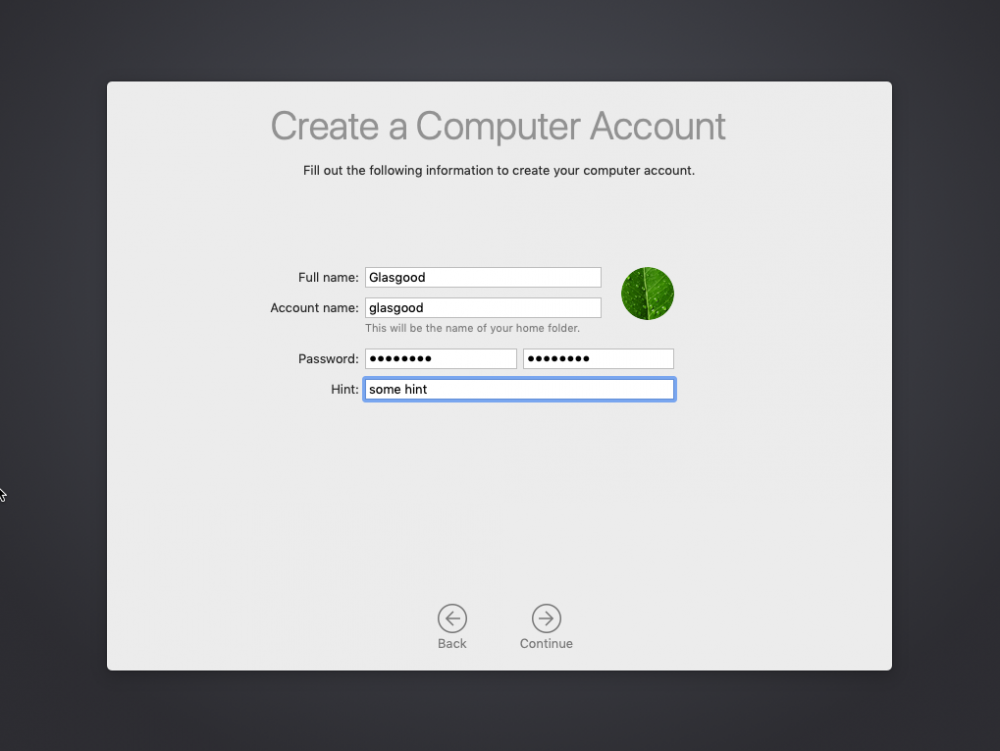

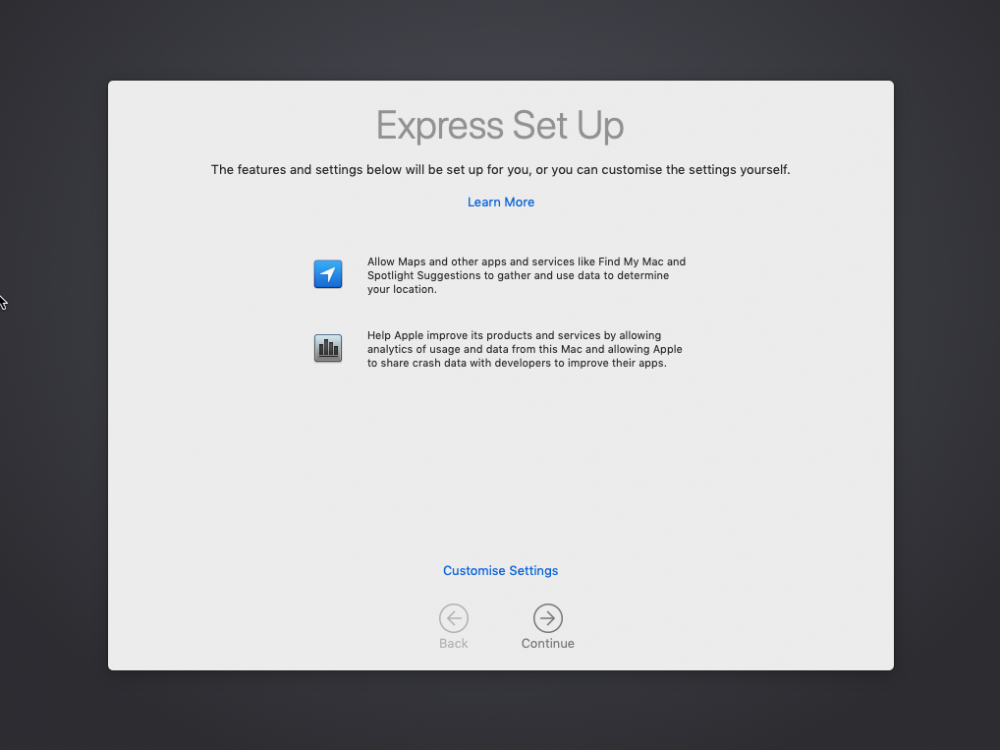

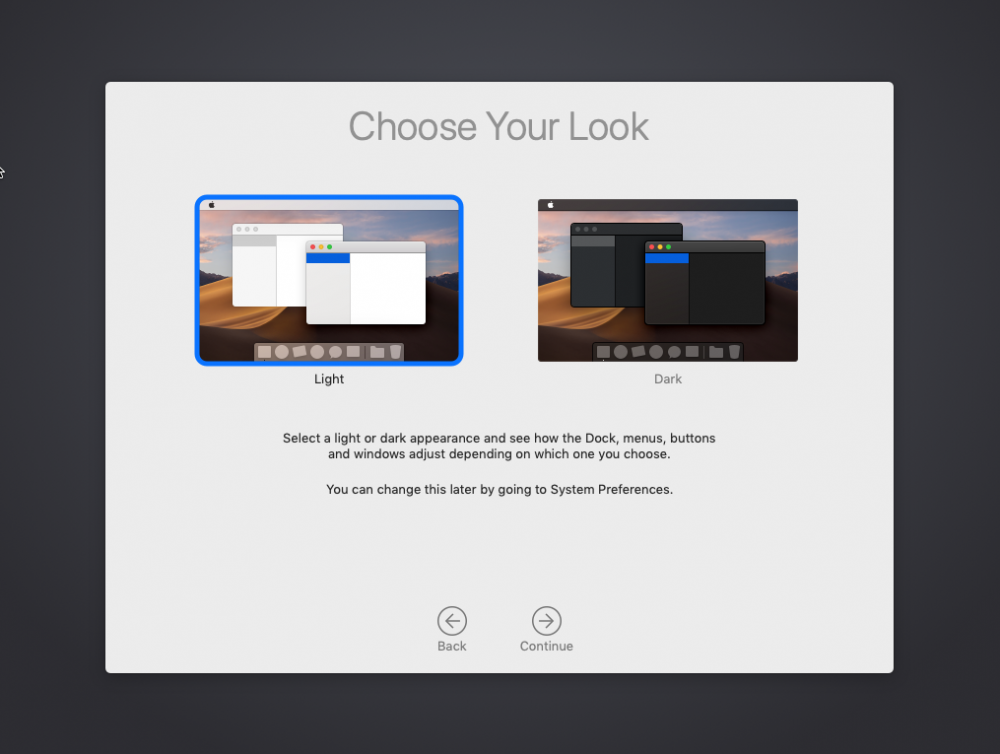

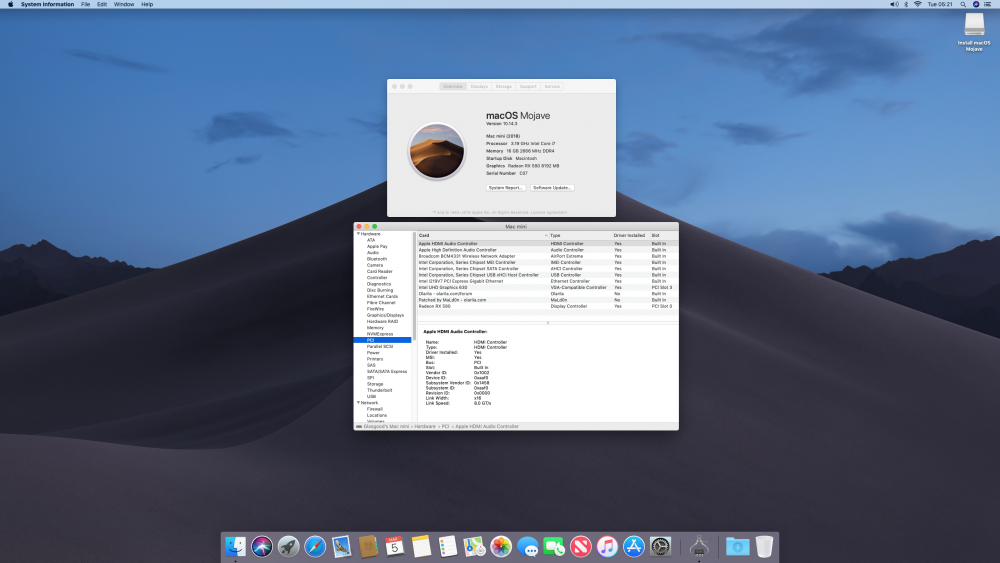

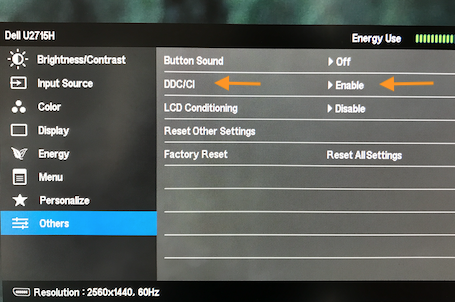

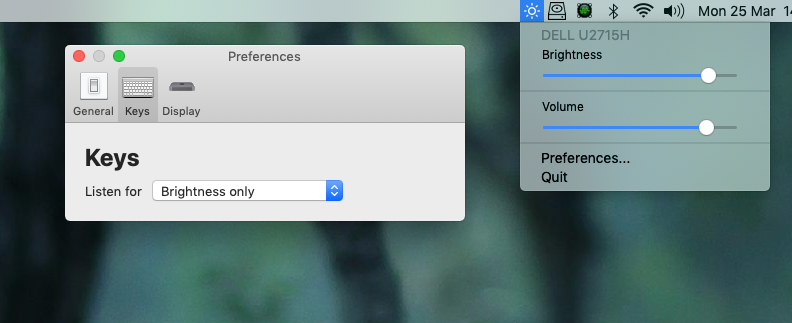

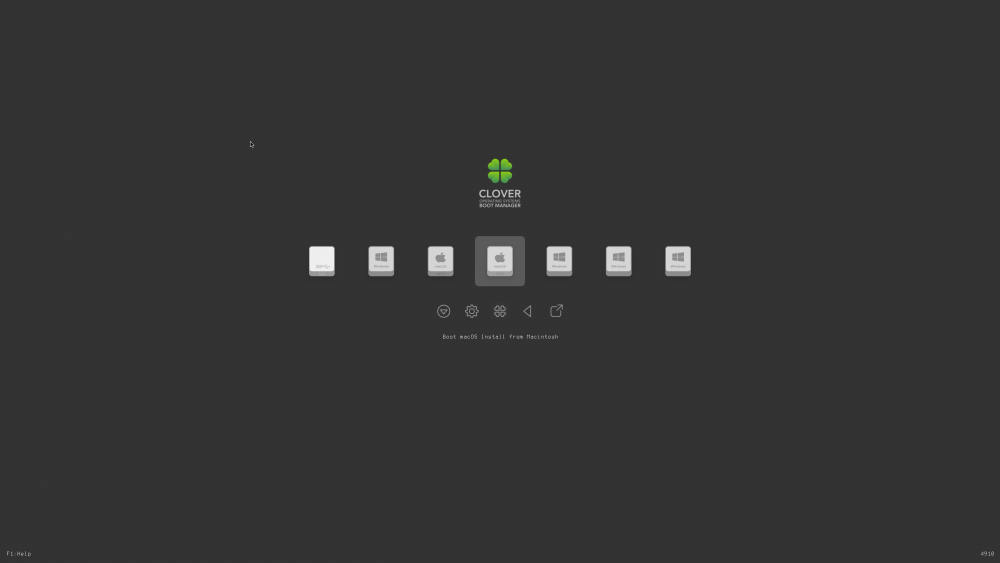

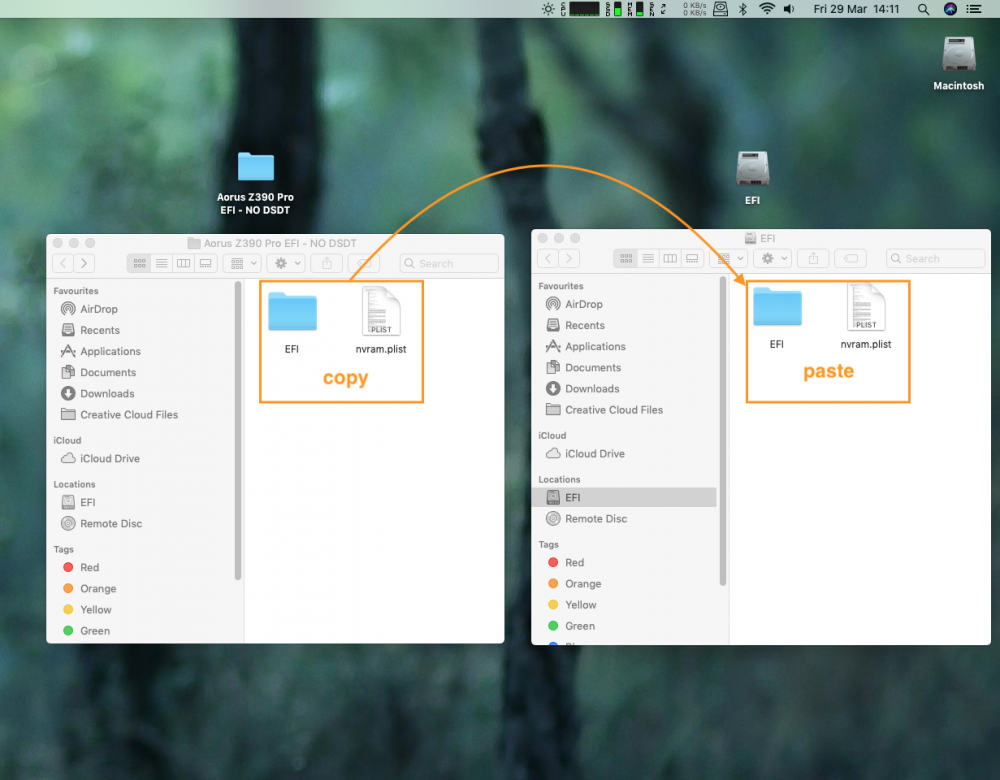

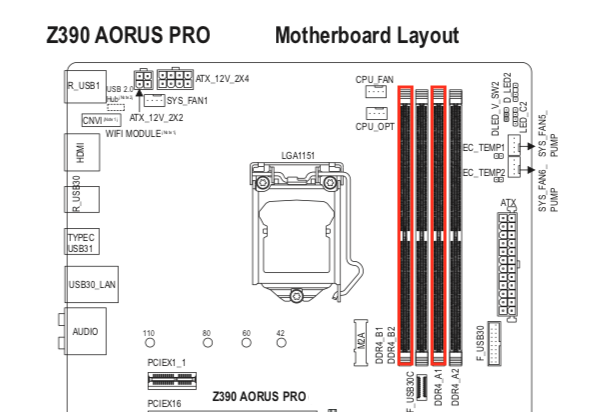

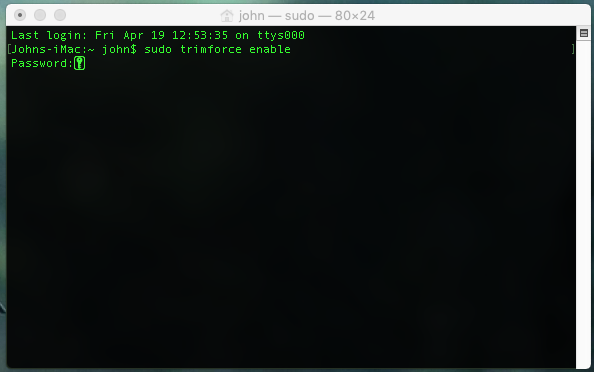

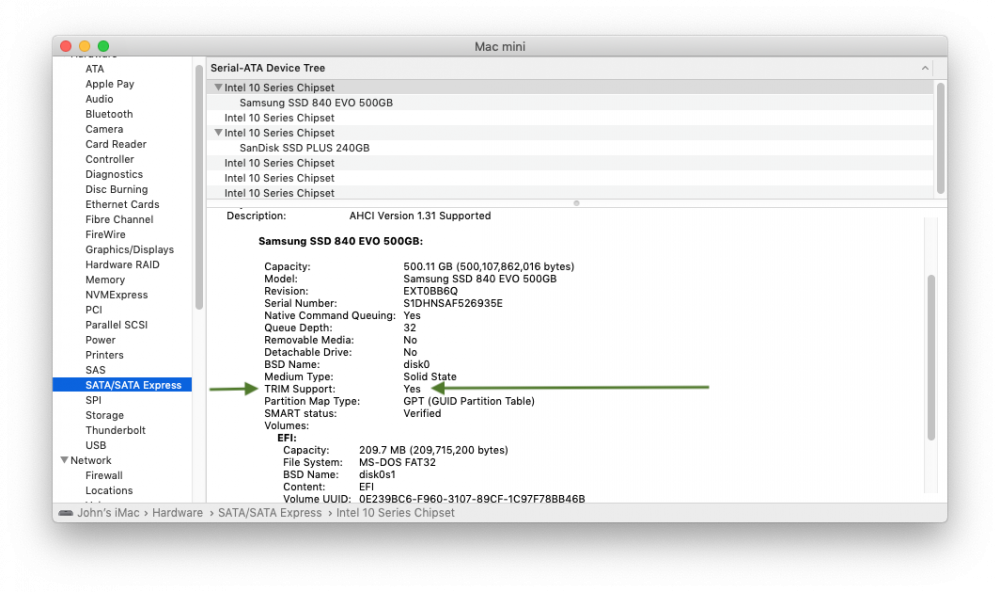

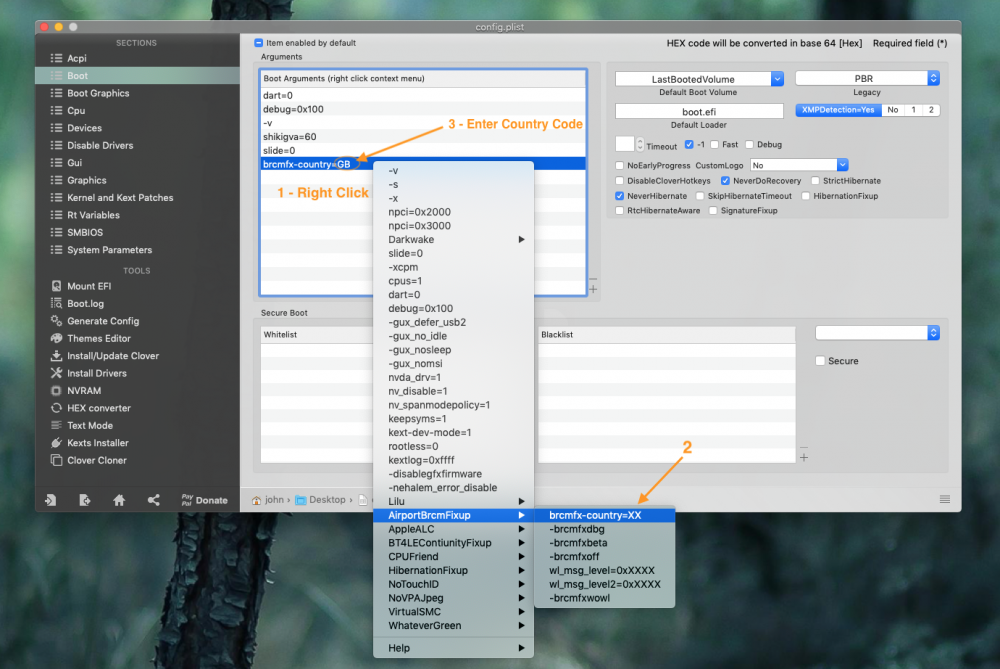

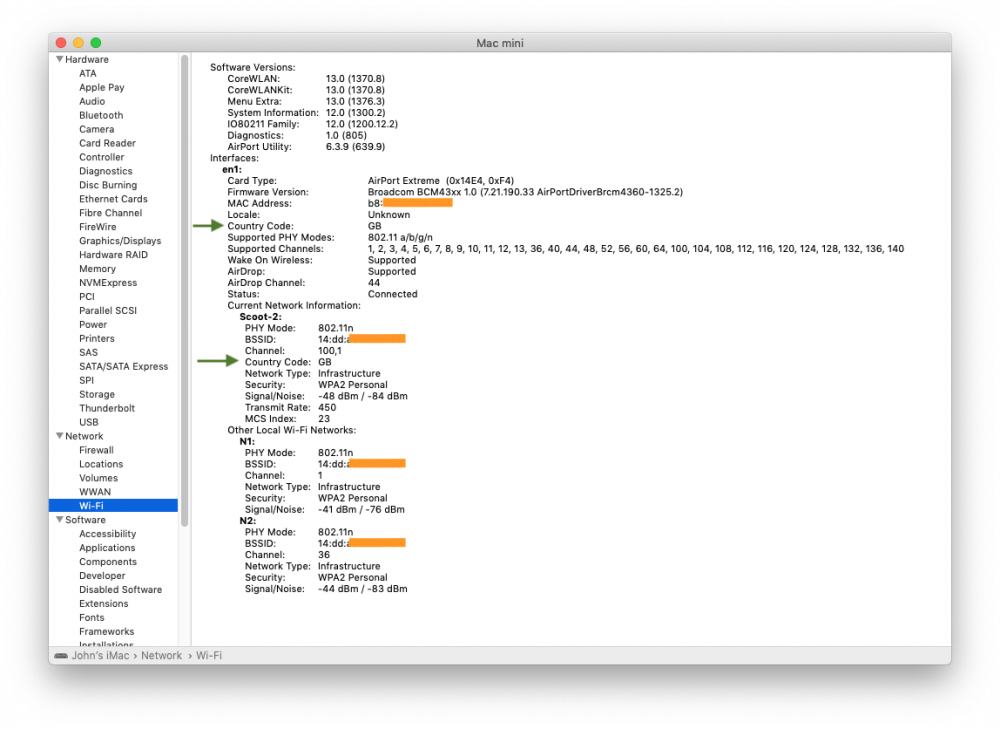

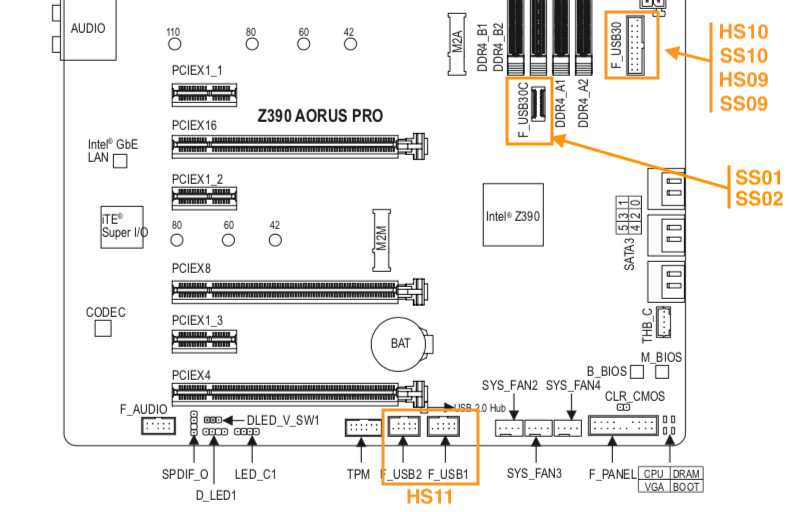

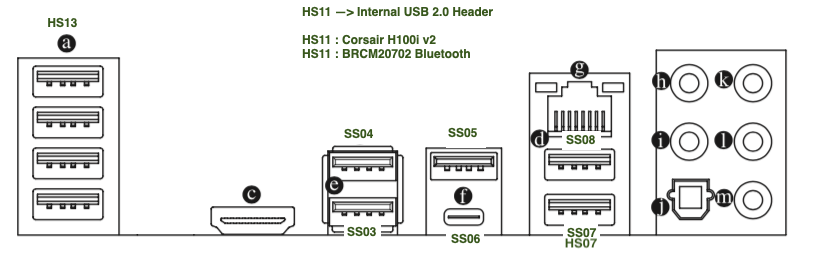

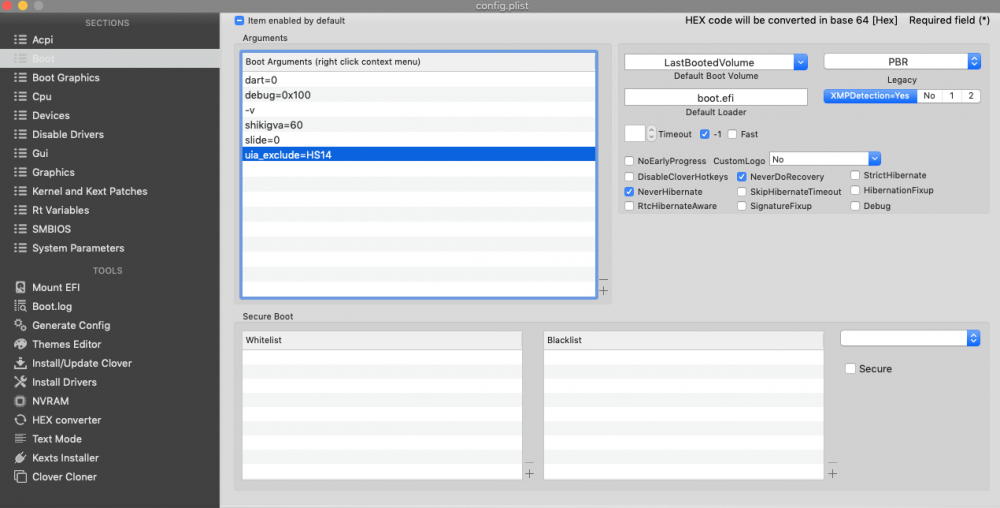

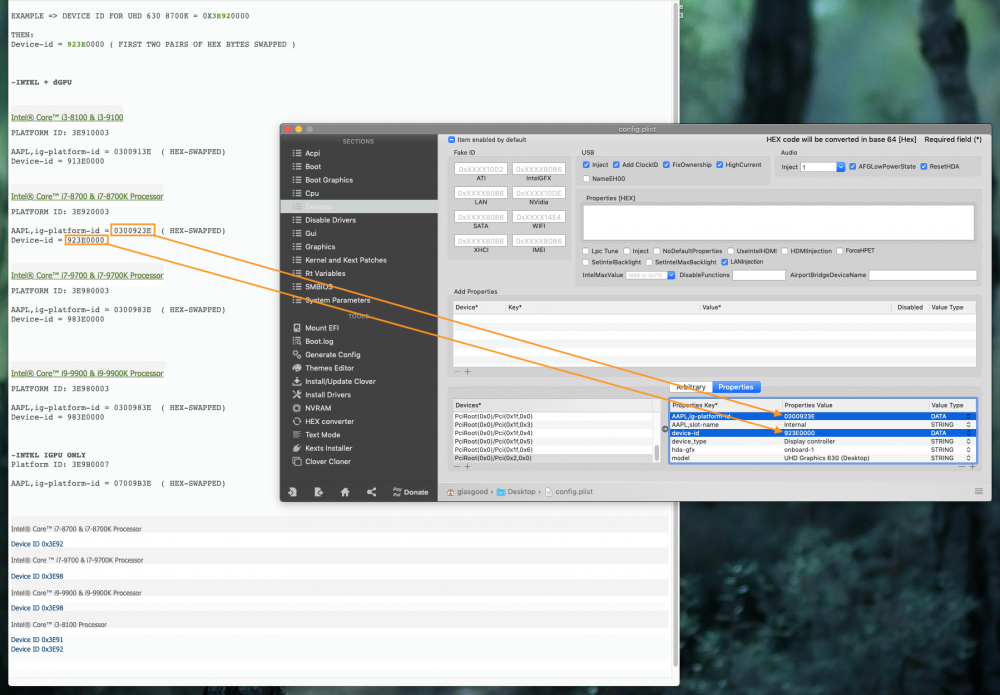

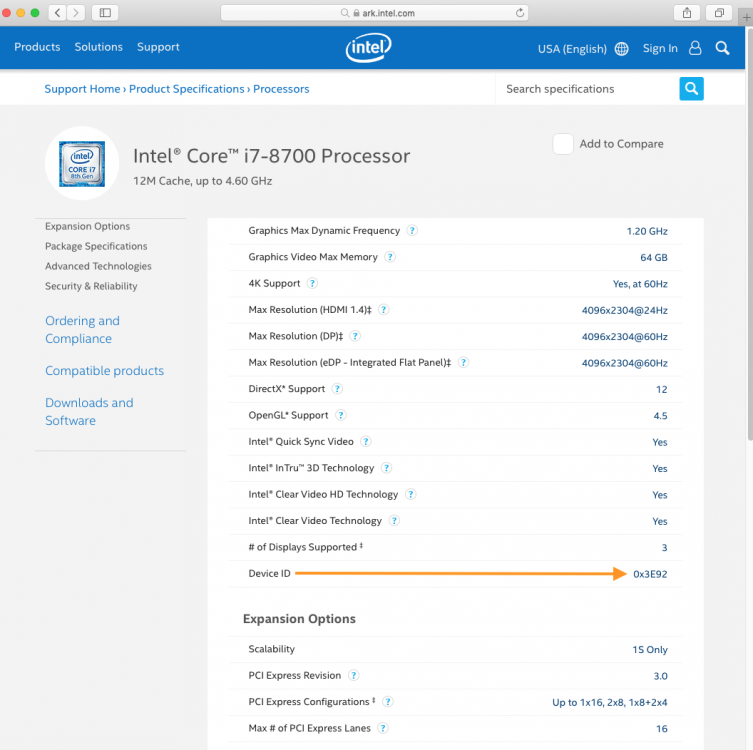

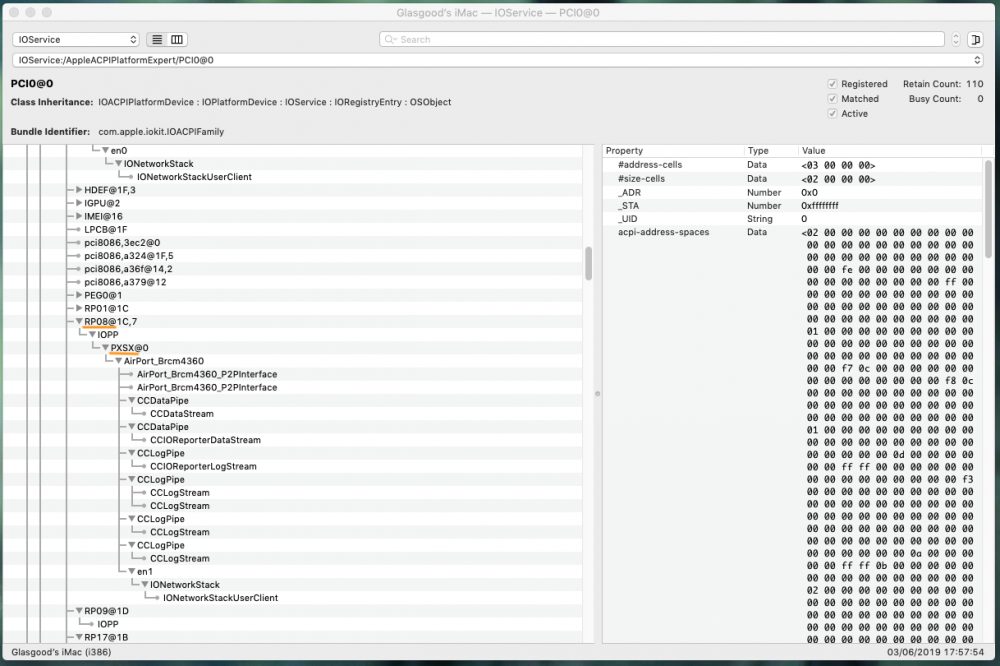

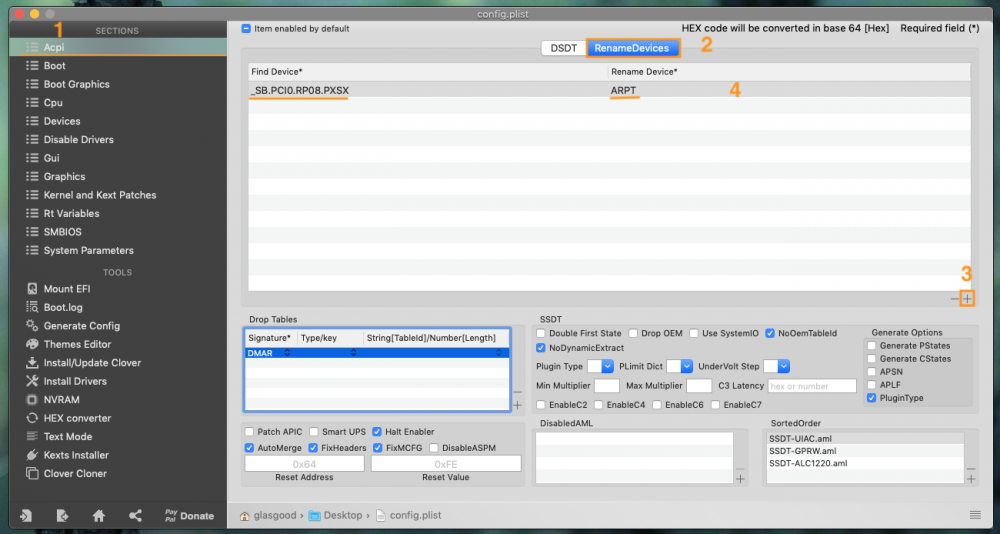

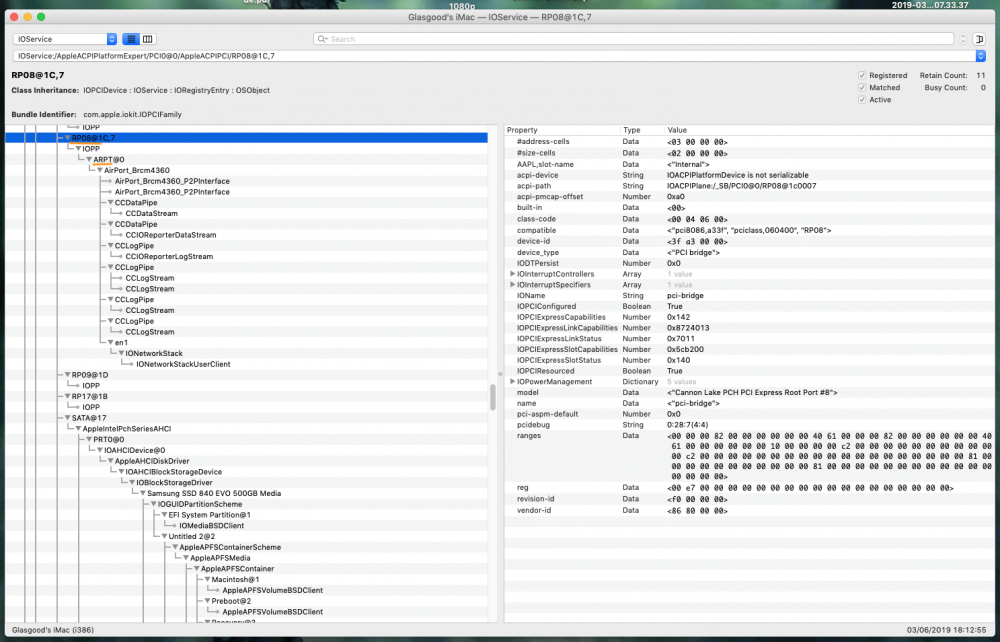

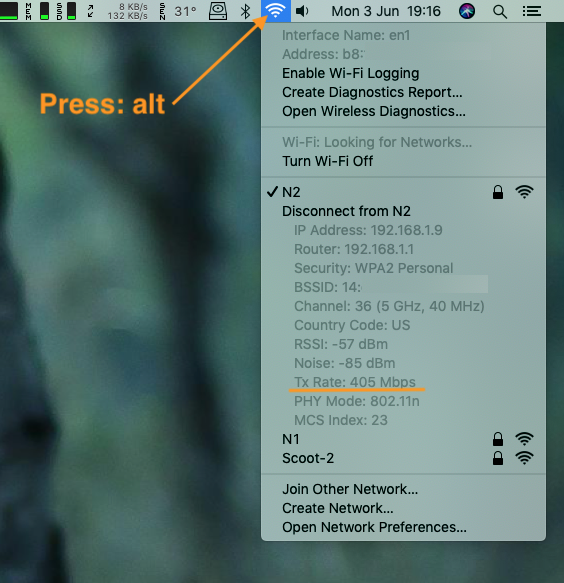

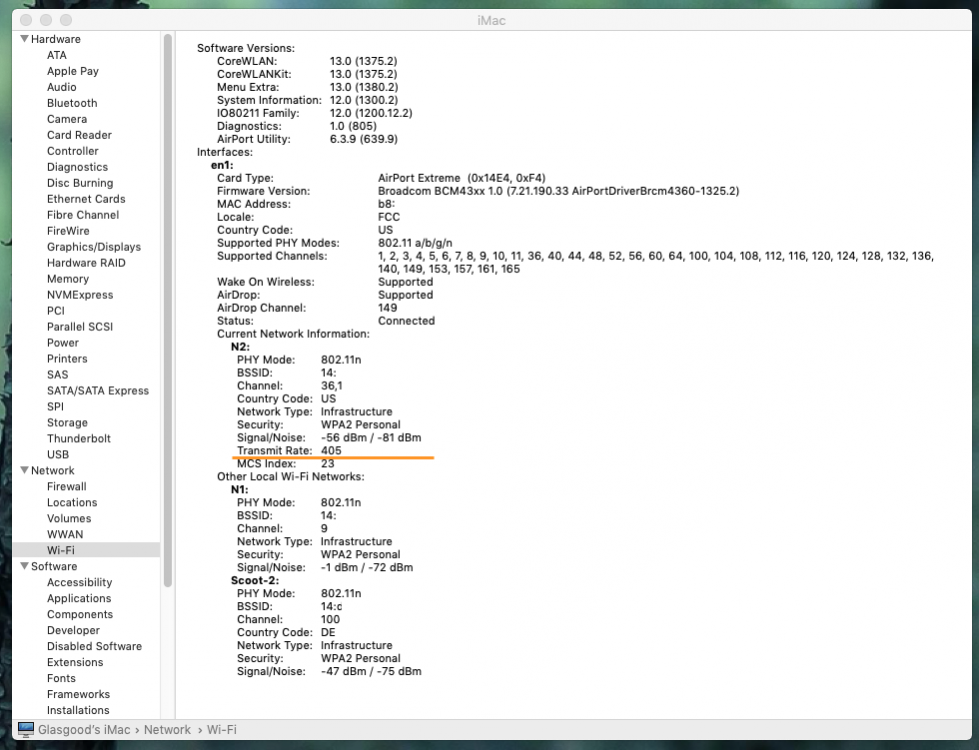

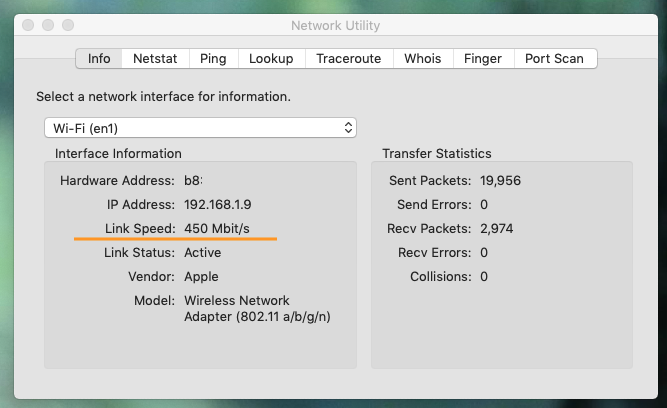

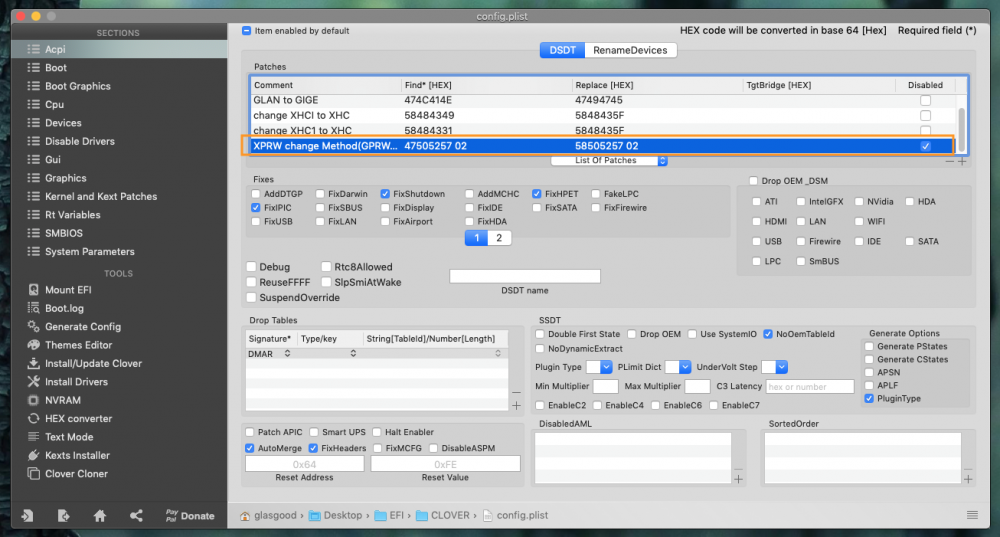

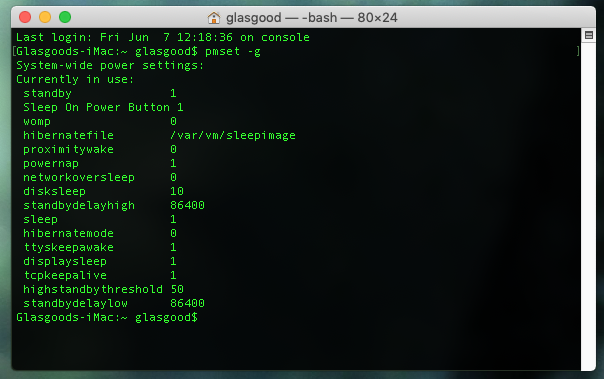

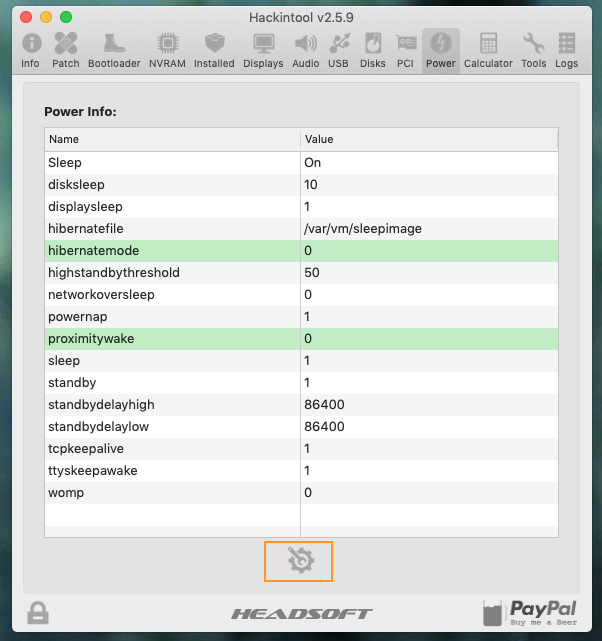

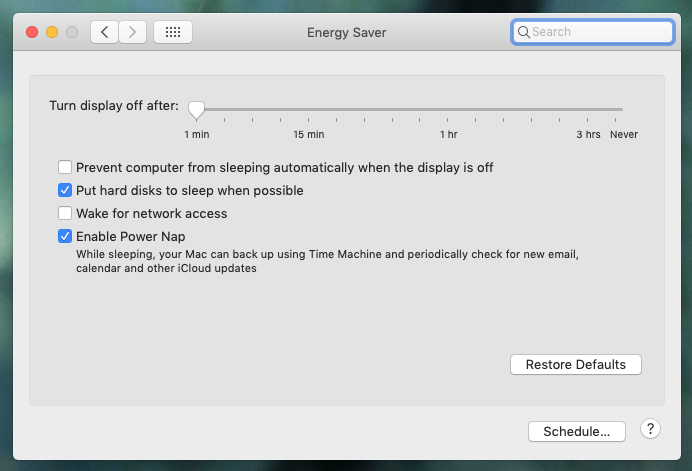

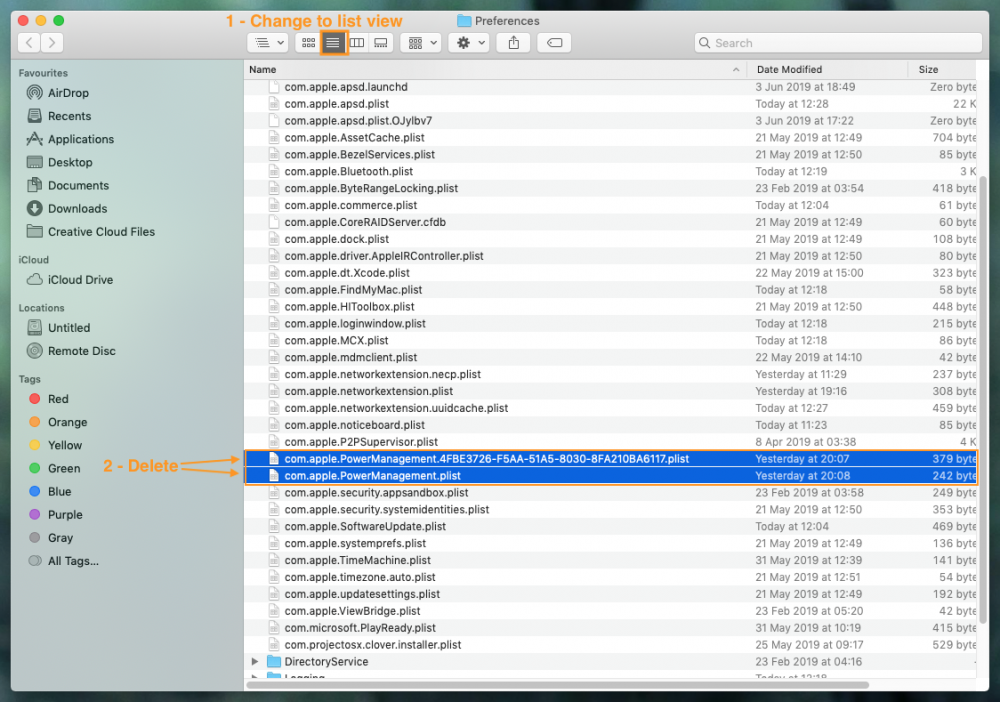

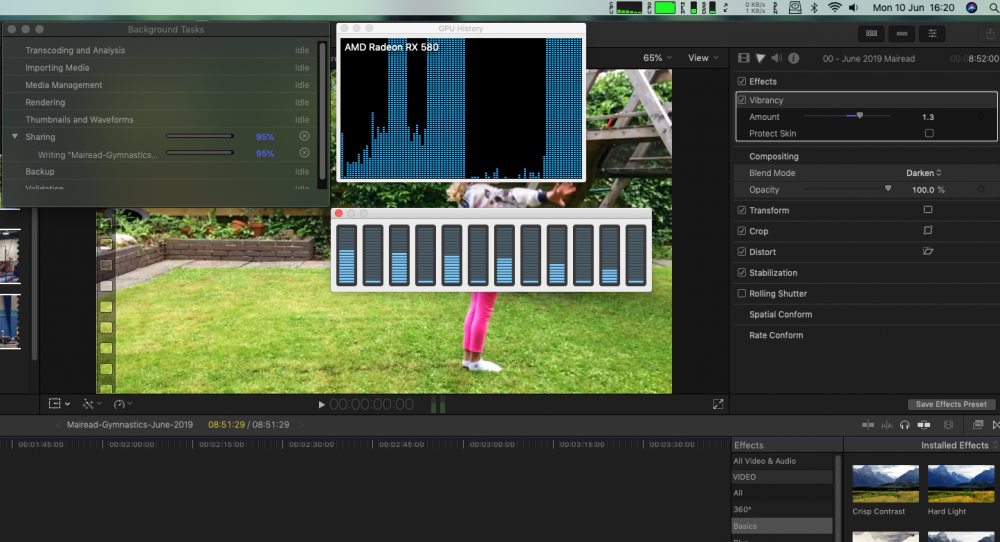

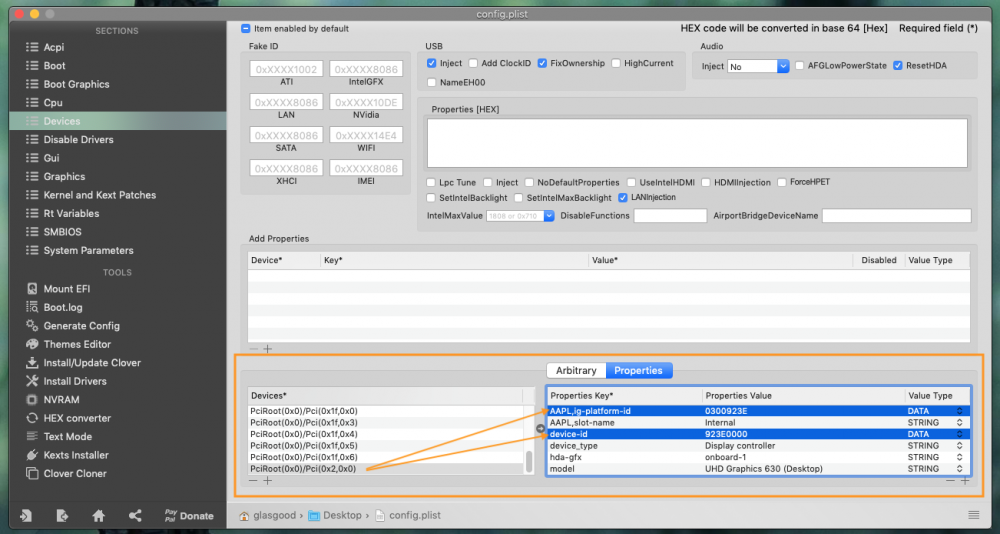

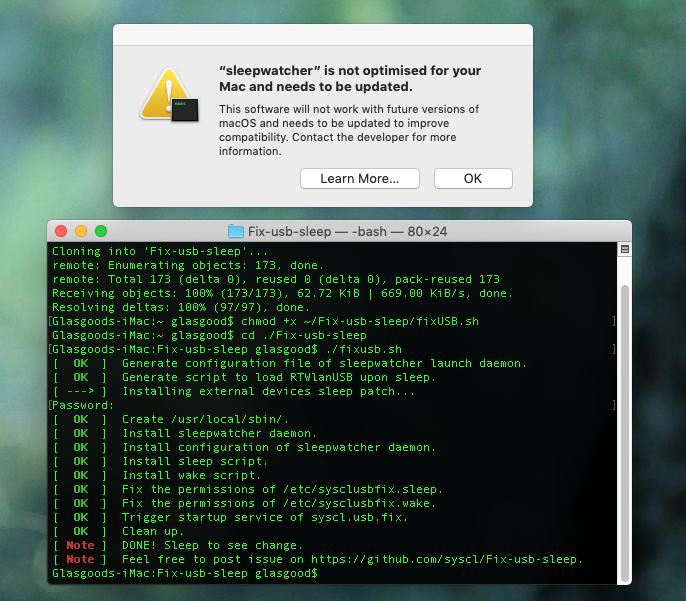

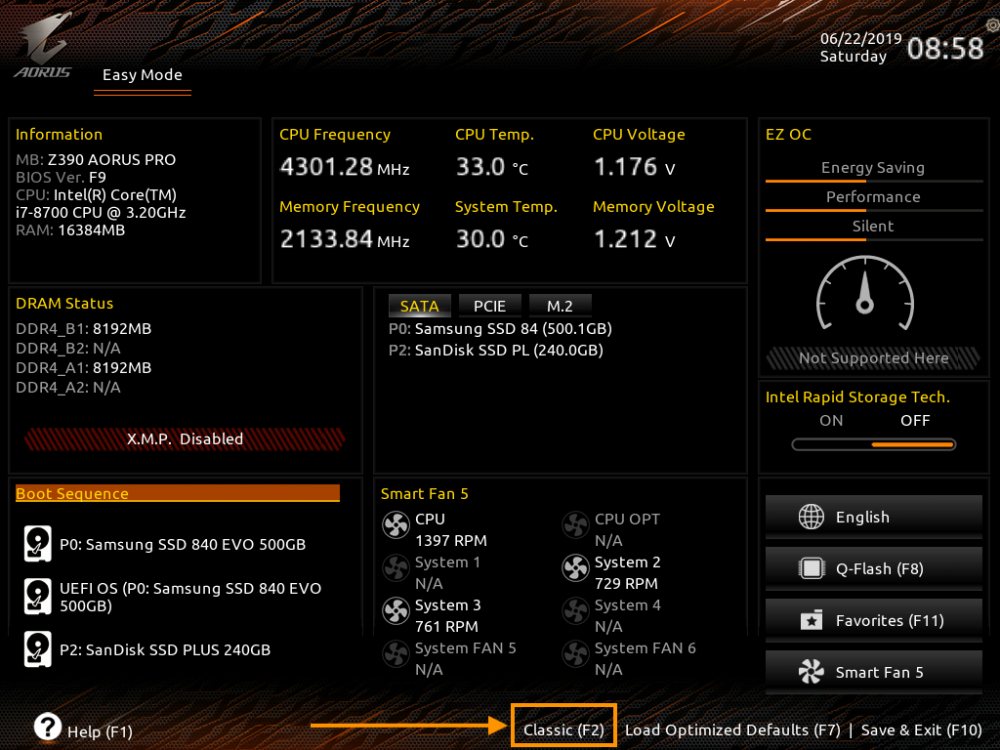

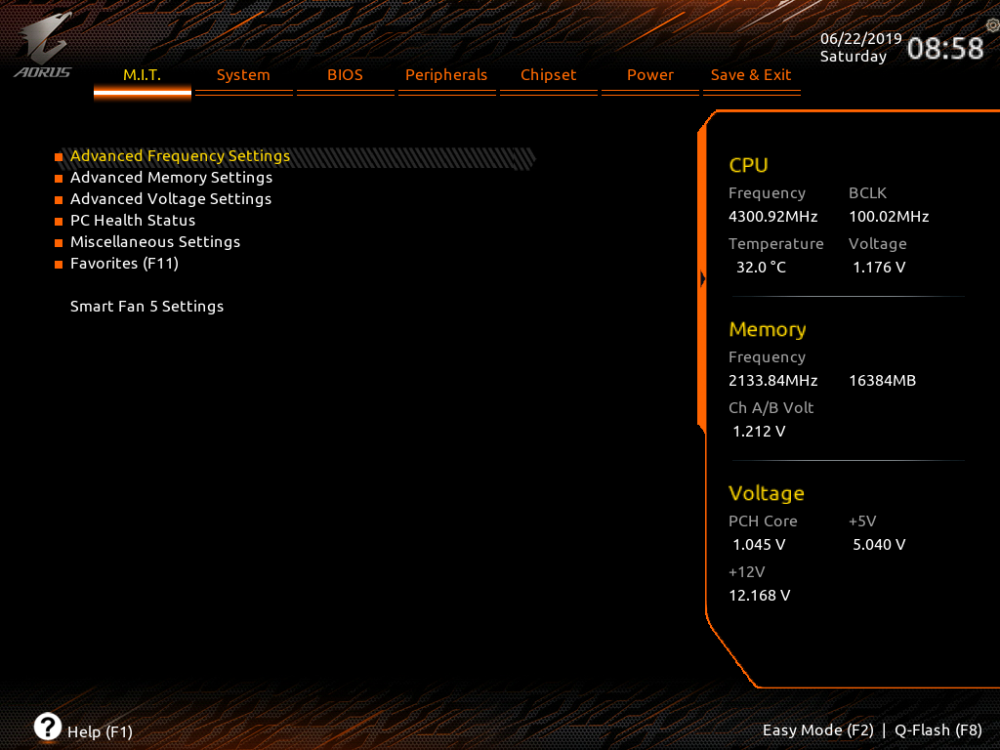

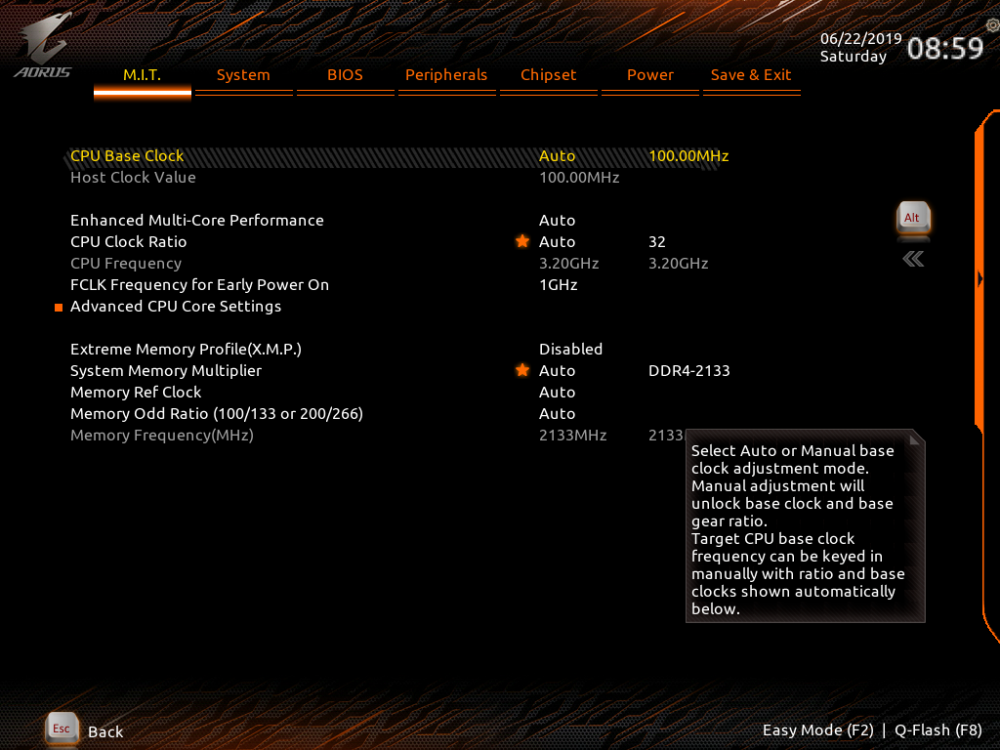

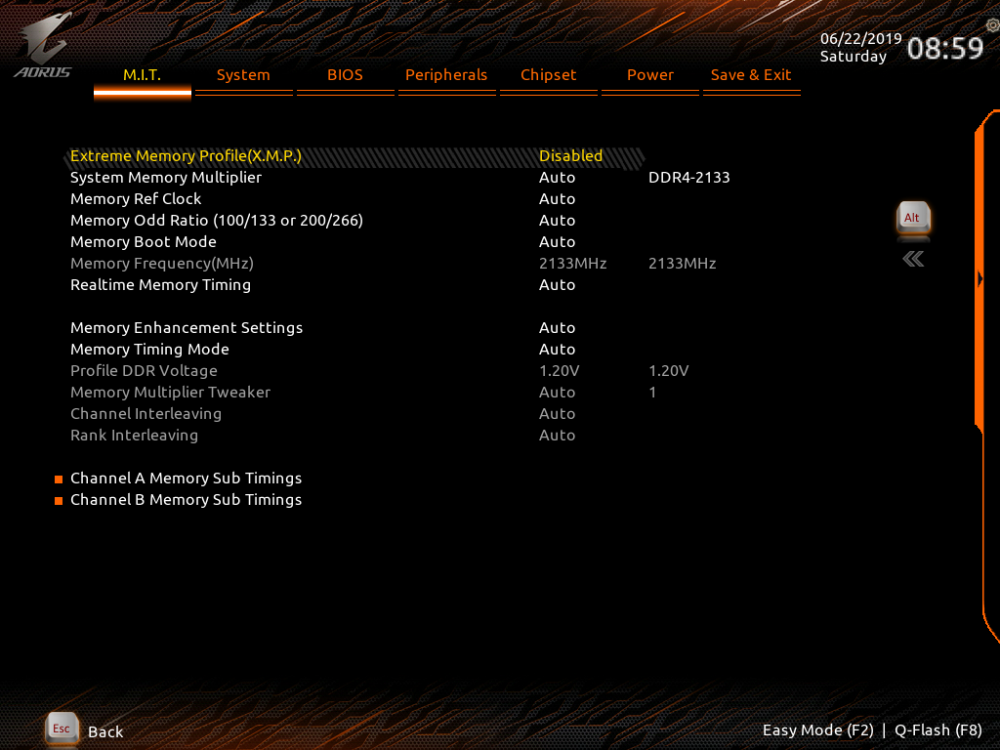

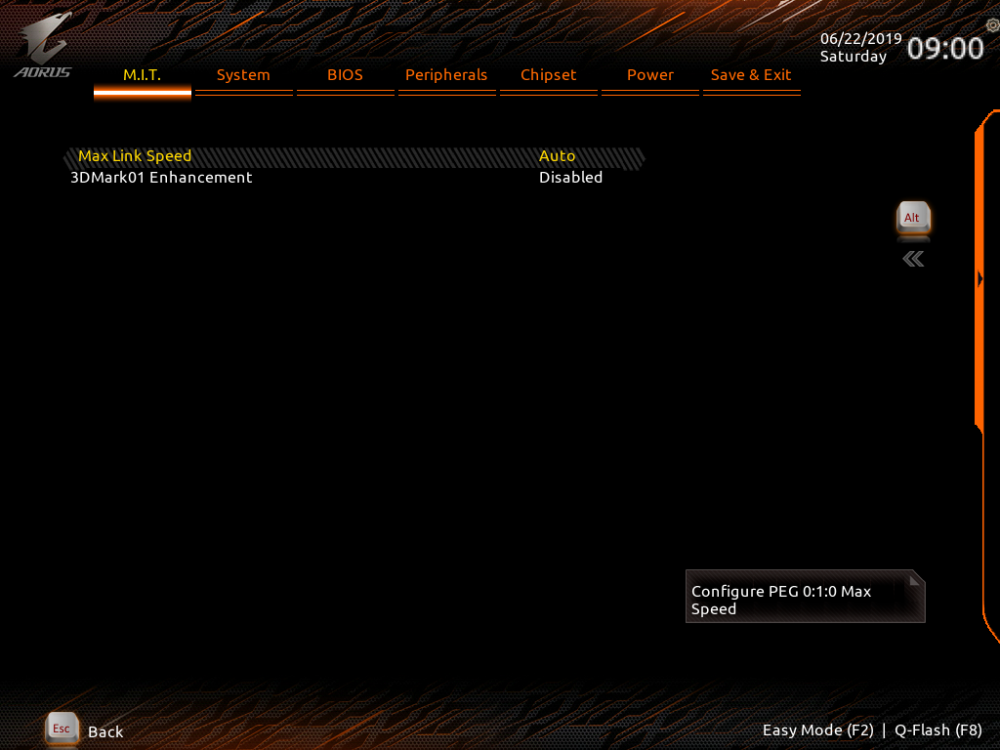

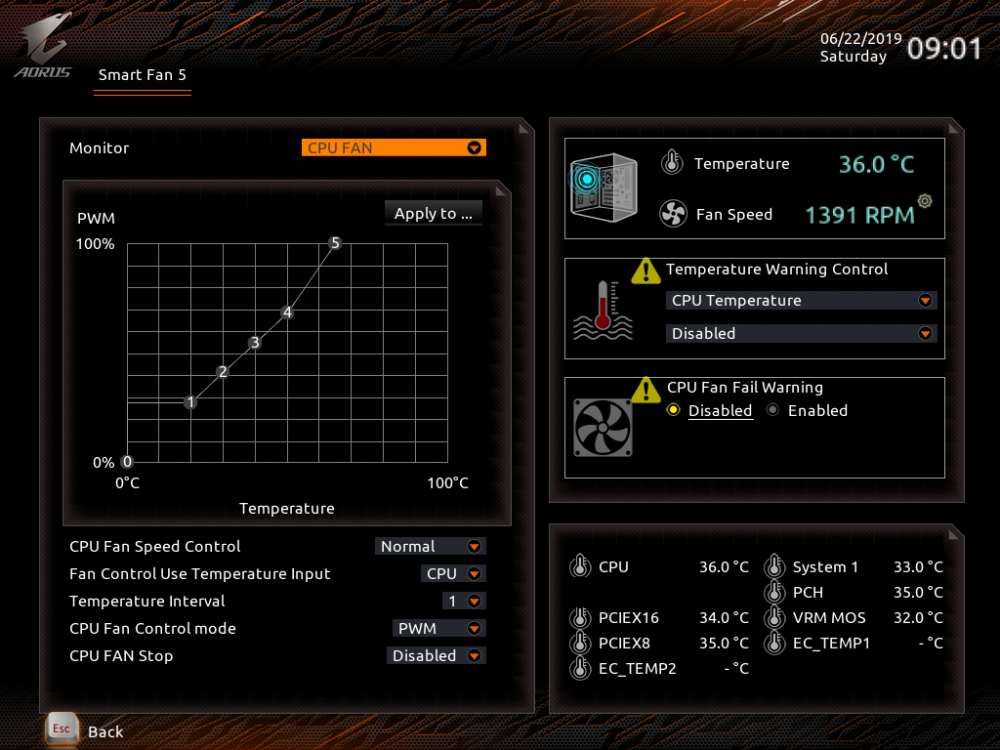

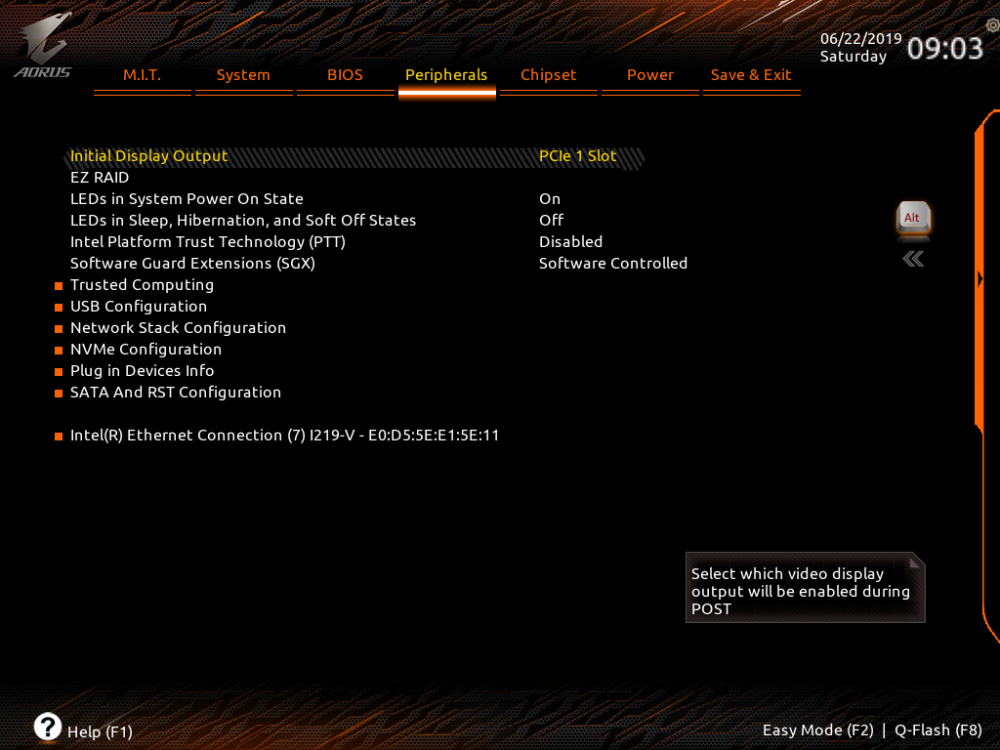

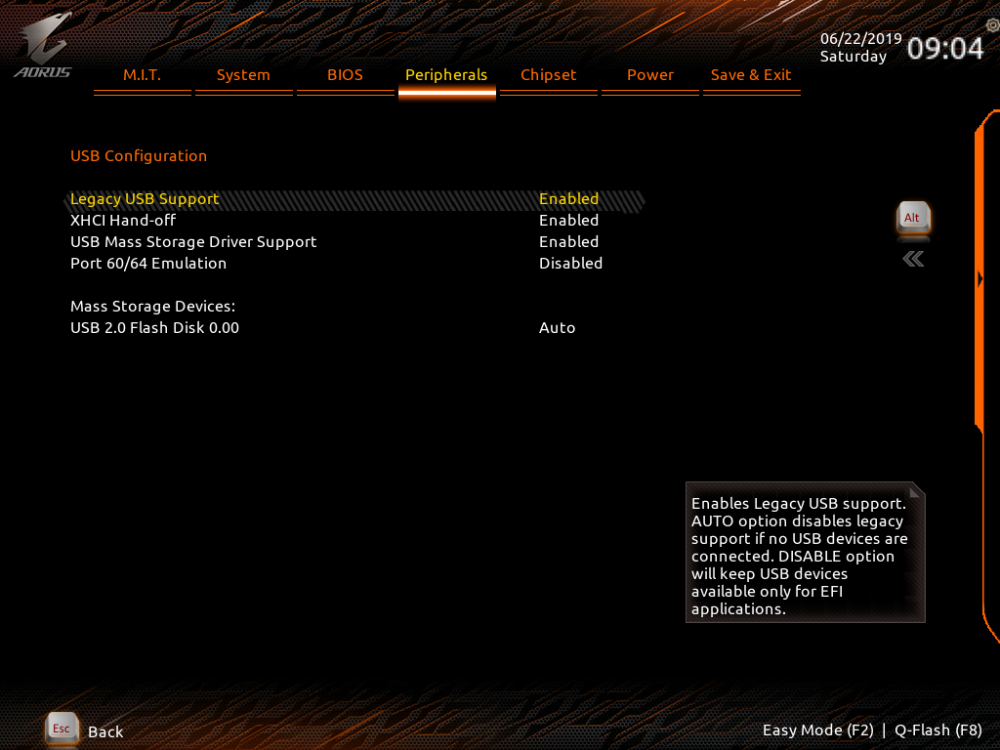

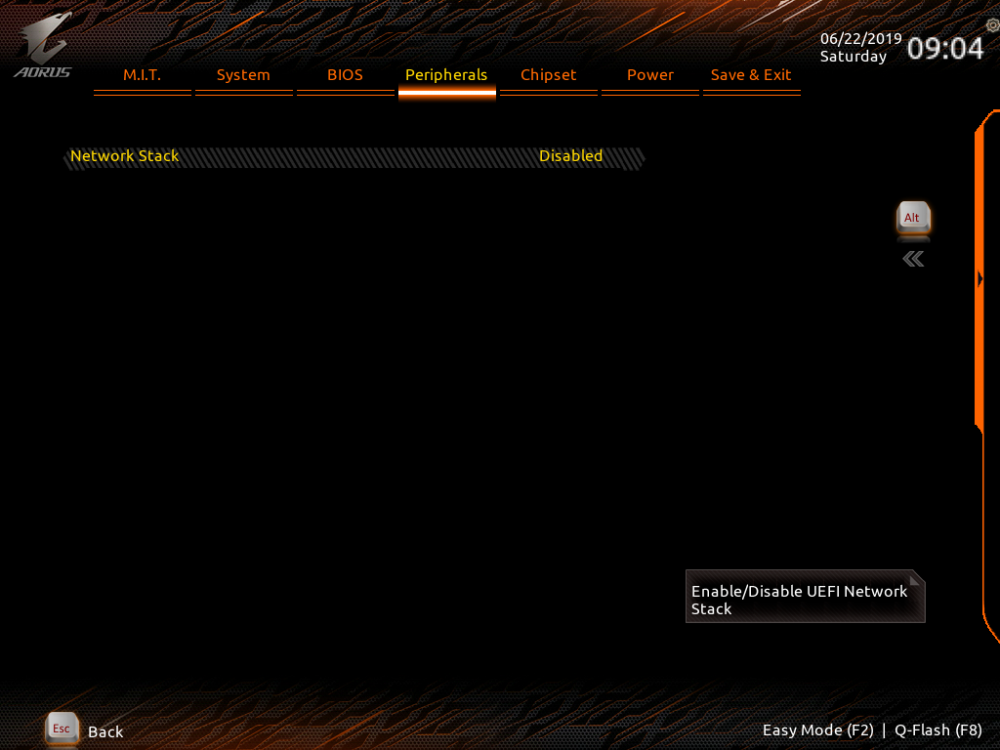

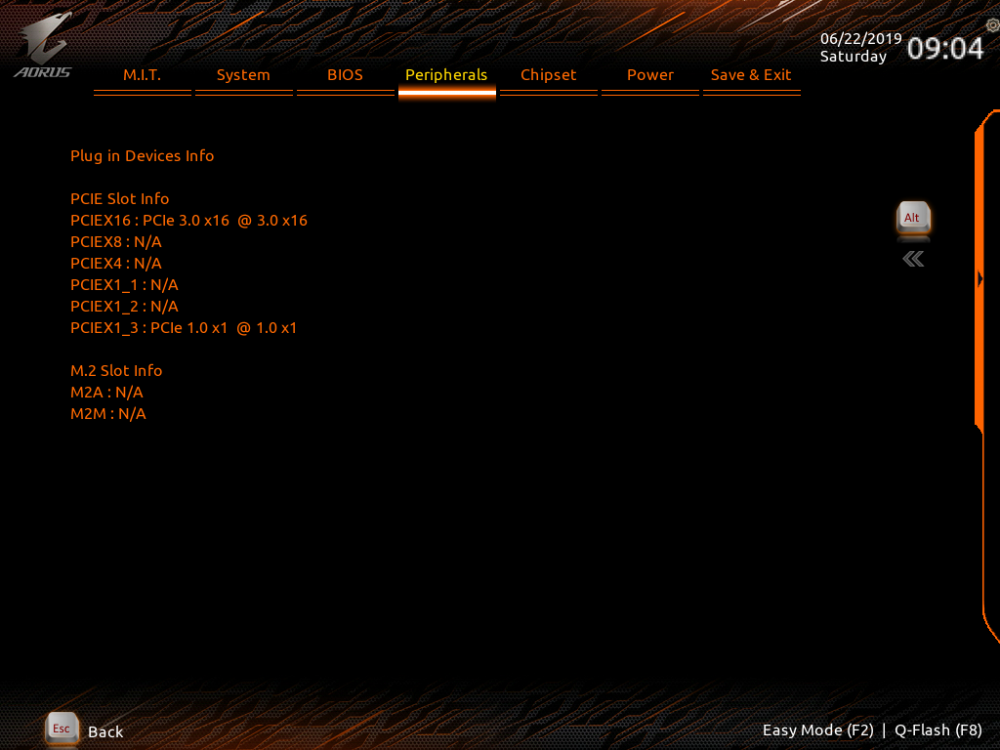

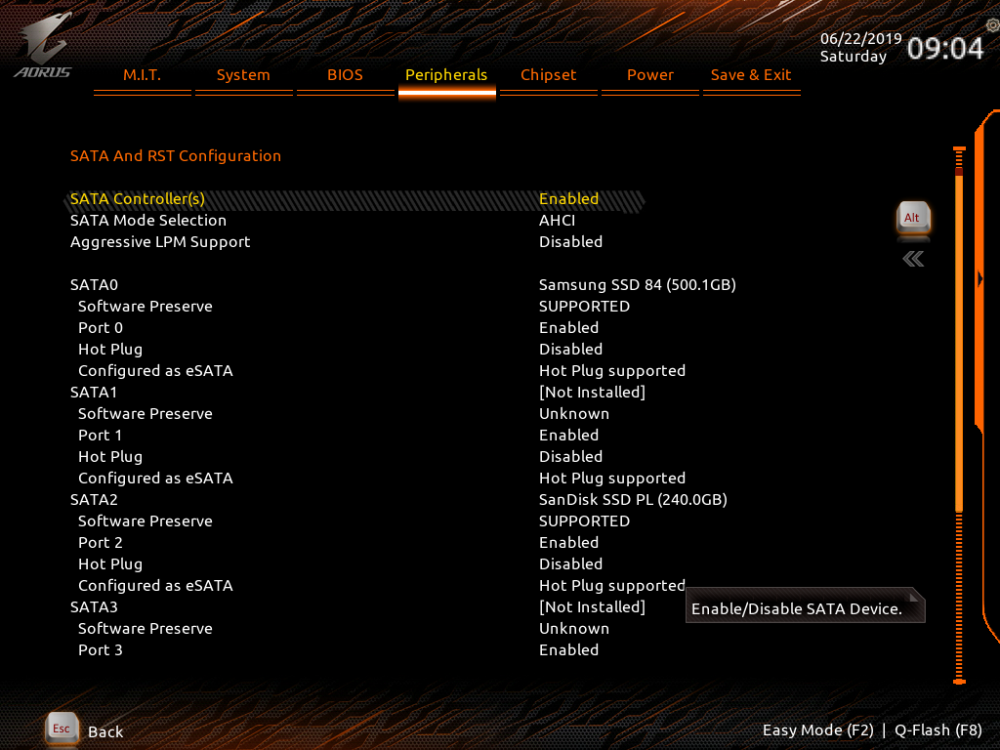

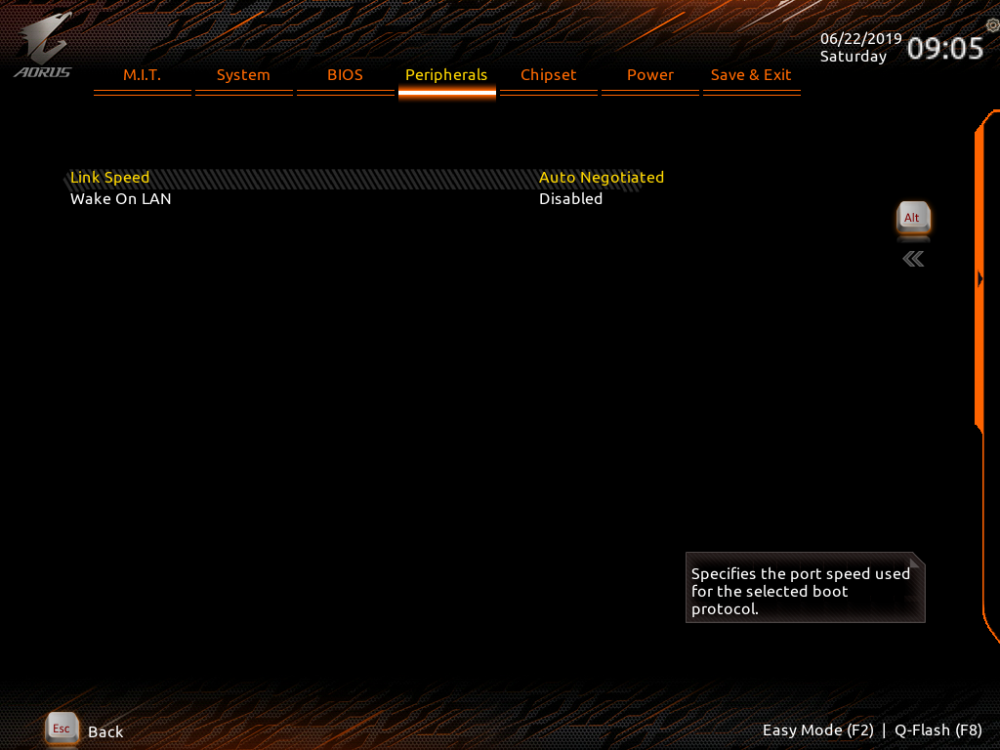

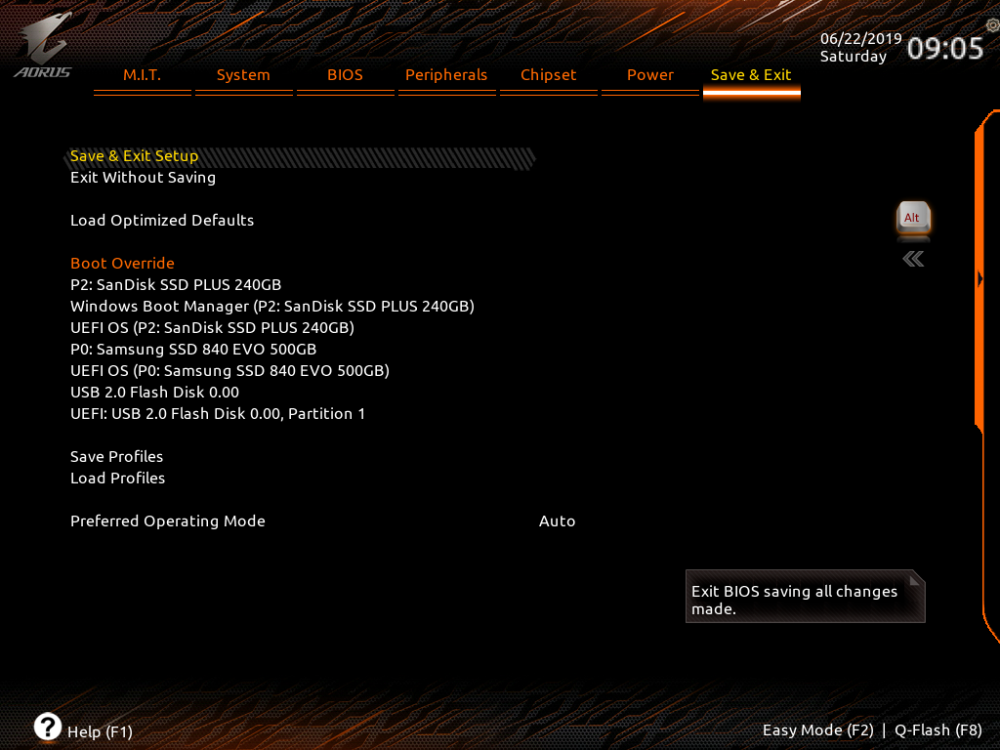

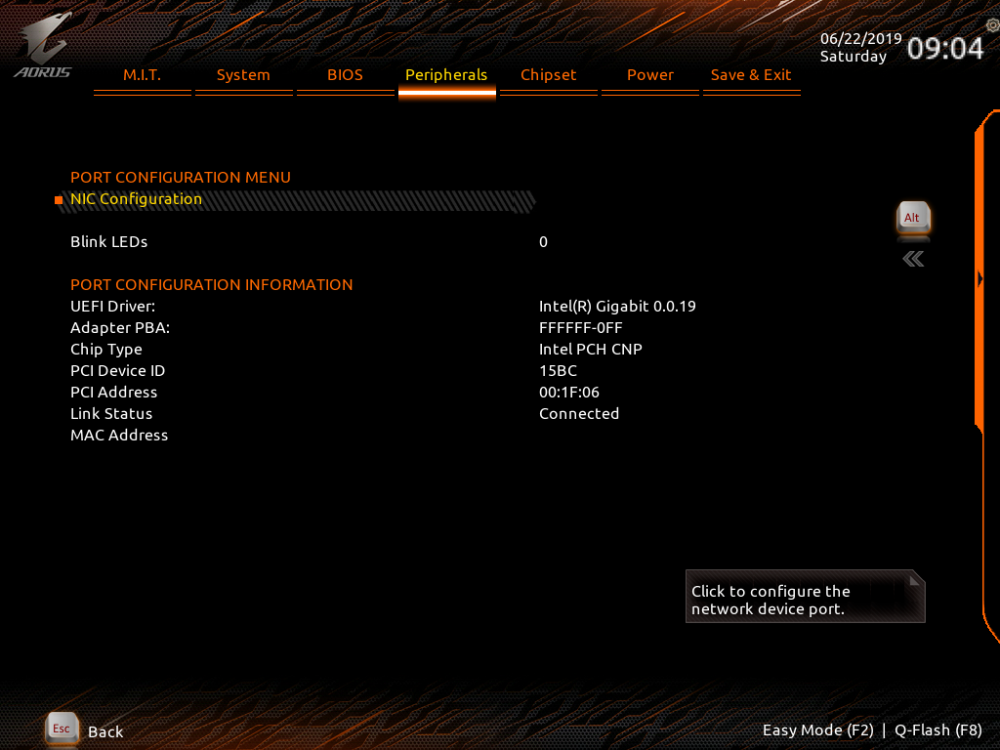

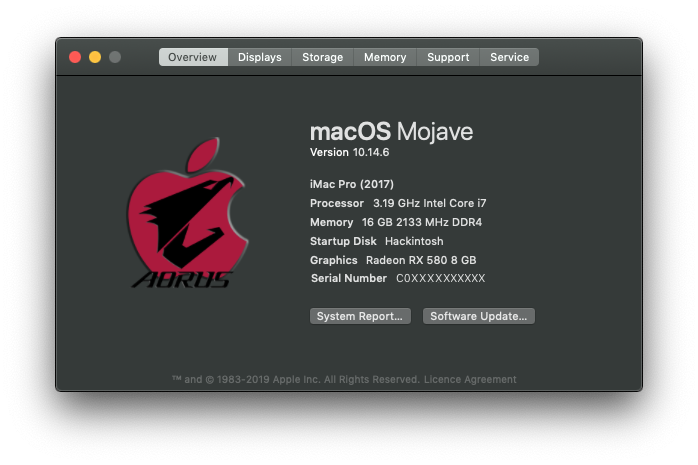

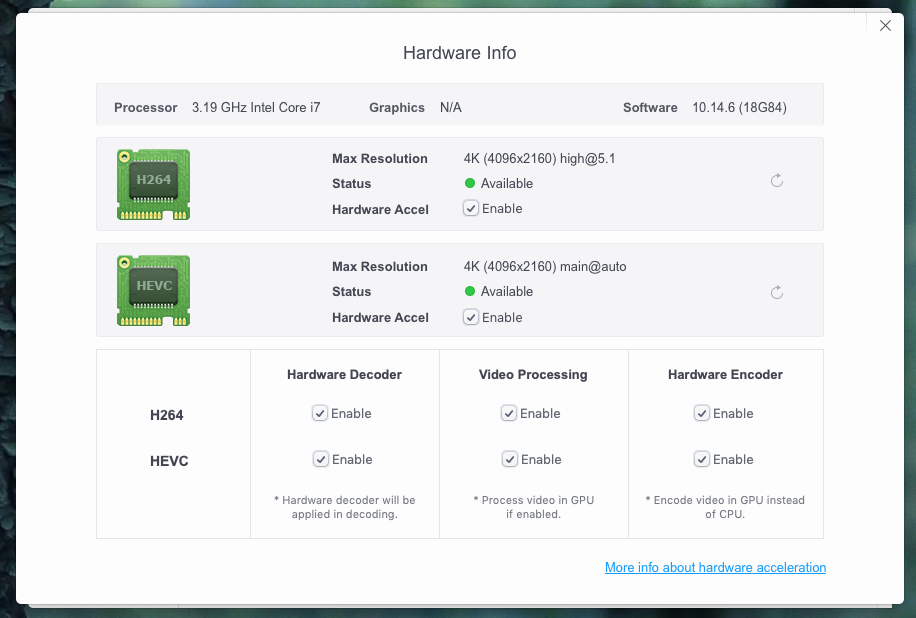

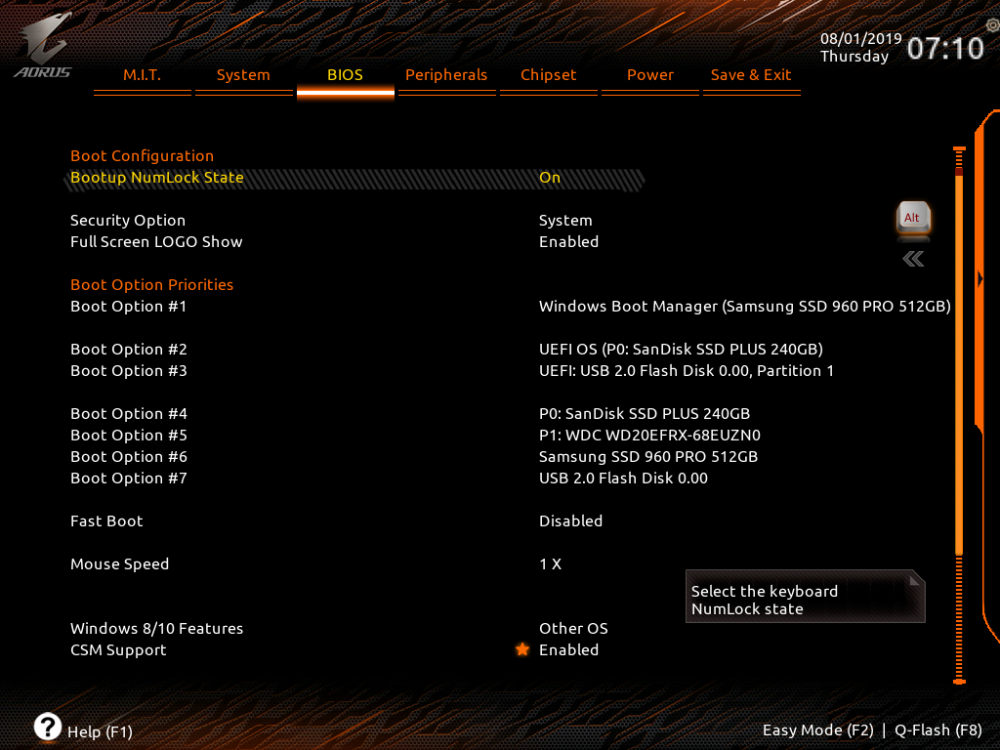

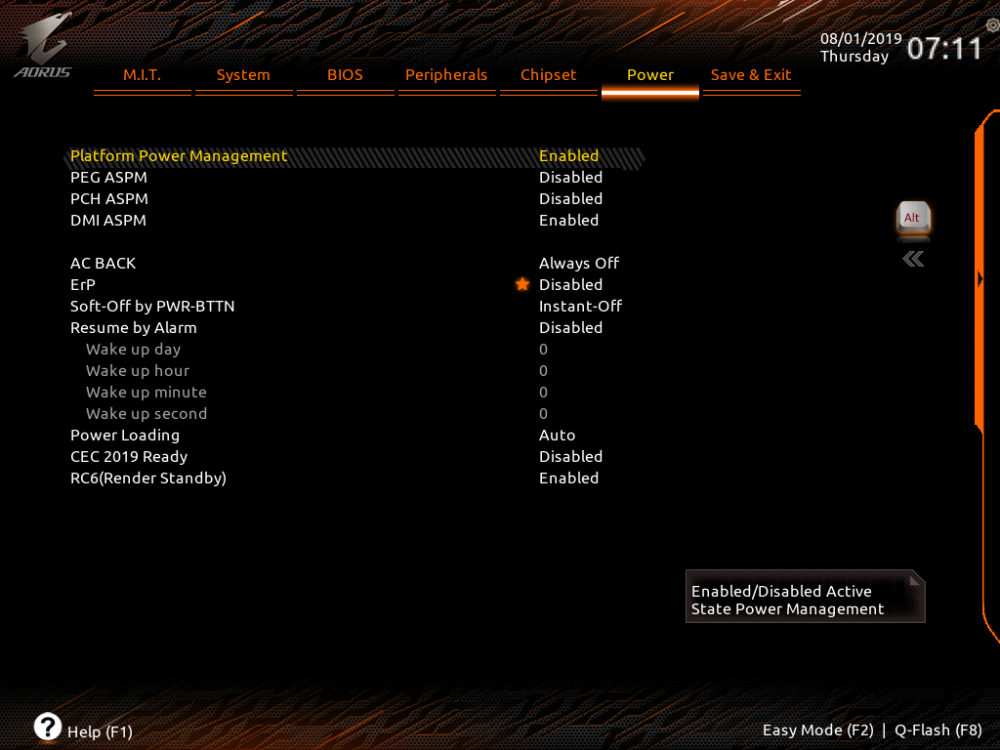

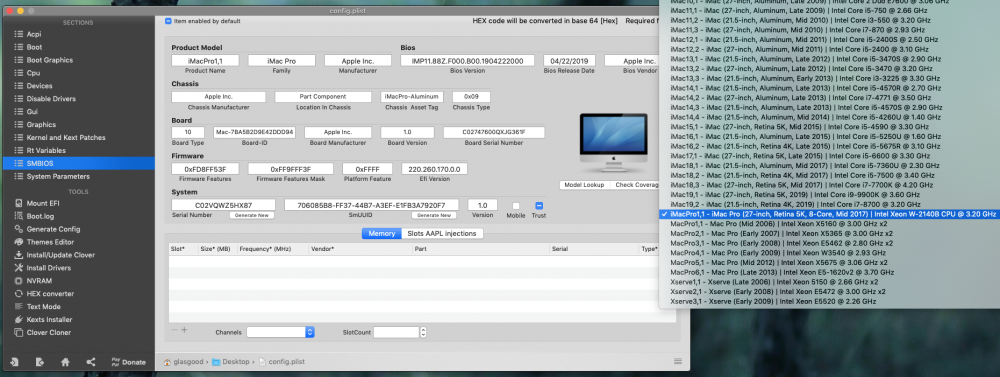

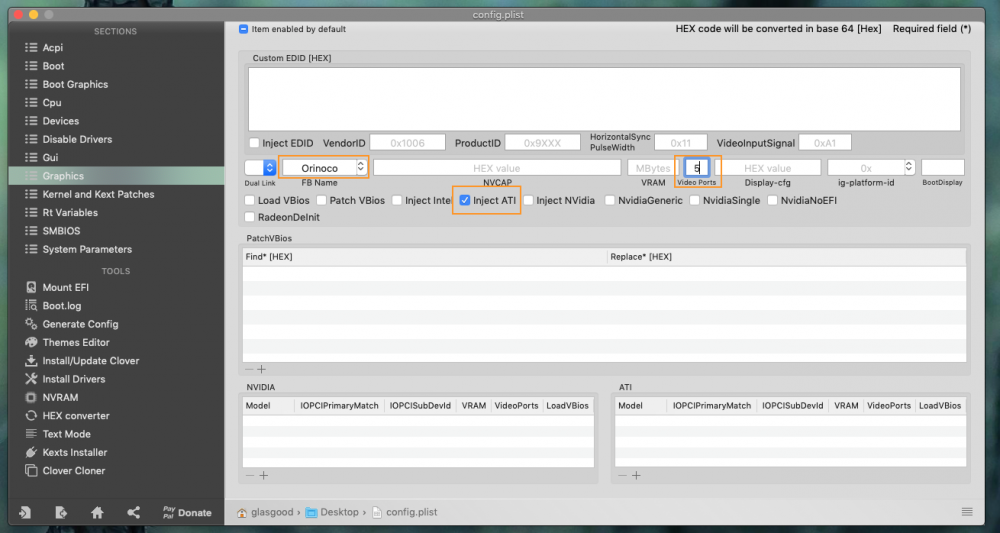

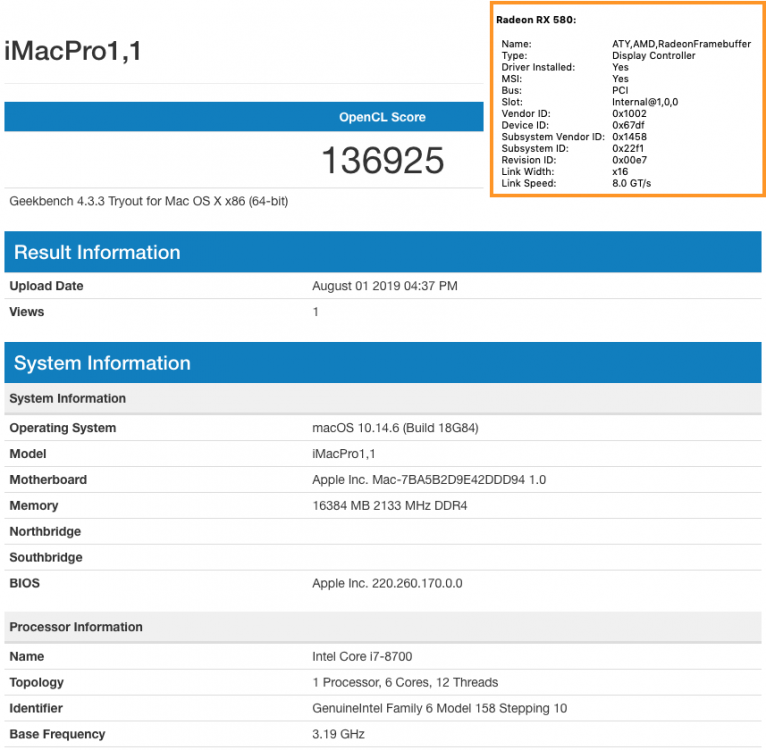

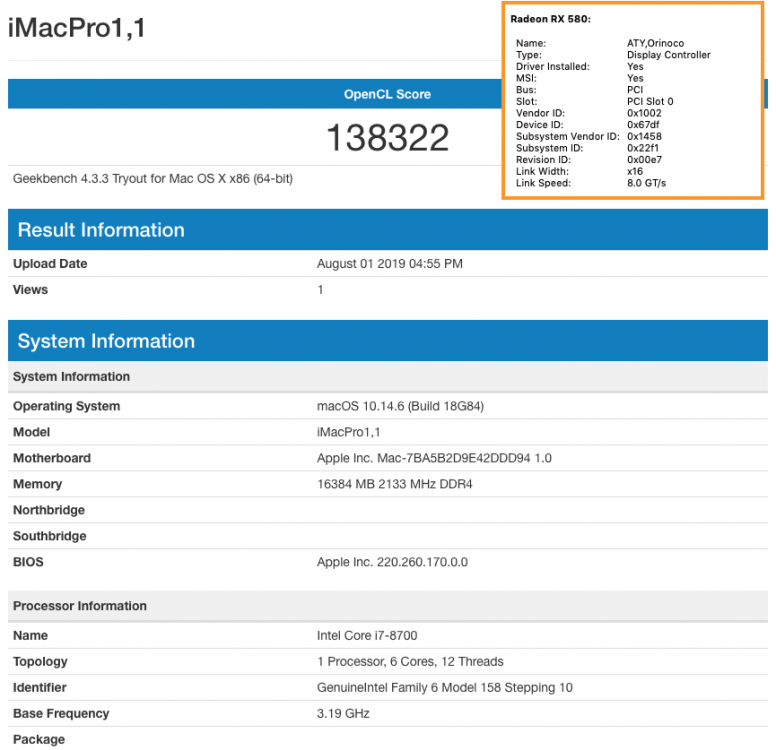

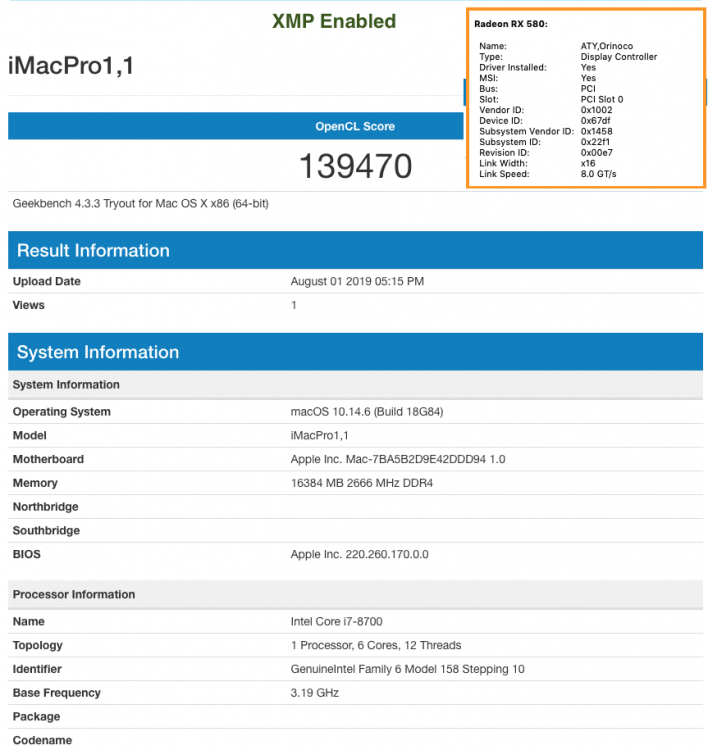

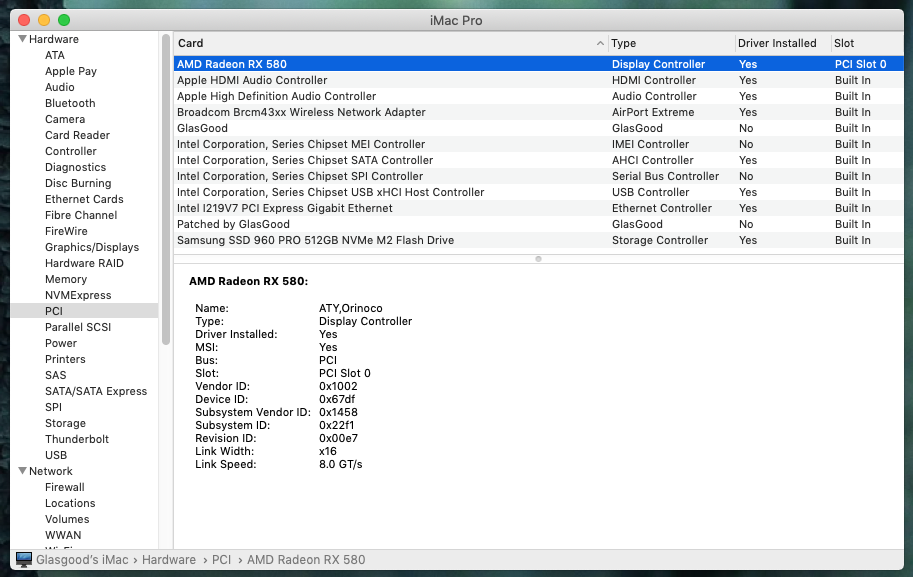

GLASGOOD'S MOJAVE HACKINTOSH GUIDE For latest EFI for macOS Catalina and discussions, visit @AudioGod's ==> Aorus Pro Z390 Patched DSDT mini guide GIGABYTE AORUS PRO Z390 CREDITS & THANKS @MaLd0n His help with EFI configuration and DSDT CLOVER TEAM Slice, Kabyl, usr-sse2, jadran, Blackosx, dmazar, STLVNUB, pcj, apianti, JrCs, pene, FrodoKenny, skoczy, ycr.ru, Oscar09, xsmile, SoThOr, rehabman, Download-Fritz, Zenit432, cecekpawon Et al APPLEALC Acidanthera, vit9696 VOODOOHDA autumnrain, slice2009, zenith432 ESP PRO MOUNTER @Micky1979 HACKINTOOL @headkaze CLOVER CONFIGURATOR Mackie100 THEME ENGINE Alex Zielenski INSANELYMAC OLARILA Hackintool Tutorial daliansky Hackintosh Vanilla Desktop Guide /r/Hackintosh - corpnewt MONITORCONTROL JoniVR & theOneyouseek ------------------------------------------------------------------------------------------------------------------------------------------------------------ UPDATES ------------------------------------------------------------------------------------------------------------------------------------------------------------ PART LIST • Intel I7 8700 • Gigabyte Z390 AORUS PRO • Gigabyte AORUS RADEON RX 580 8GB ( connected to monitor with DisplayPort ) • Corsair Vengeance LPX 16GB ( 2 x 8GB ) 2666MHz – CMK16GX4M2A2666C16 In this build, both memory modules are installed in memory slots DDR4_A1 and DDR4_B1 • Corsair RM650x 80 Plus Gold Power Supply Unit • Corsair H100i V2 AIO Hydro/Water RGB LED CPU Cooler • Samsung EVO 500GB SSD (2.5) macOS Mojave • Samsung EVO 250 GB SSD (2.5) Windows 10 Pro • NZXT H500 Mid Tower ATX Case • 1st RECOMMENDED WIFI CARD → ABWB BCM943602CS 802.11AC WI-FI With Bluetooth 4.0 PCI-Express (PCI-E) OR • 2nd RECOMMENDED WIFI CARD → WIFI and Bluetooth with BCM94331CD with PCI-e adapter (but will require AirportBrcmFixup.kext for AirDrop.. ) WORKING • Sound • Ethernet Port • WiFi • SSD Trim • USB 3.0 & 2.0 • AirDrop • iCloud • Hardware Acceleration AMD RX 580 / AMD Vega • iMessages • Facetime • Handoff • Netflix on Safari browser • Continuity PREAMBLE - BEFORE YOU START Here detailed, is all the steps towards building a successful and stable Aorus Pro Z390 Hackintosh, if you are a first time Hackintosher, this guide will have you quickly up and running with the Aorus Pro Z390 Hackintosh. To rule out potential problems from the go, only have the disc that you plan to install macOS Mojave connected to the Aorus Pro, disconnect any other Windows / Linux or data drives, external drives from your Aorus Pro. Windows / Linux and data drives can be connected after successful installation of macOS Mojave If you have more than 16 GB of memory, then install macOS Mojave with just 16GB or RAM installed, you can later add any additional memory. Install memory modules in slots DDR4_A1 and DDR4_B1. This build has a recommended Wi-Fi combo PCI-e card installed in slot PCIEX1_3 with its 9 pin USB cable attached to motherboard header F_USB2. ( ensure WiFi card is seated properly in PCIe slot and cable is firmly attached to WiFi card and motherboard header F_USB2 ) If using the Corsair H100i v2 AIO cooler with USB cable connected to motherboard header F_USB1, you will need to enable hot-patch ( explained in guide ) in config.plist for working sleep, wake from sleep will only work by pressing Power Button. Install macOS Mojave on its own physical drive, so do not try and install macOS Mojave onto a free partition on a disc that contains Windows. Remove any Thunderbolt cards, Thunderbolt card can be reinserted after installation. Double check your BIOS settings are the same as this guide. Following are unsupported / problematic • Intel Optane ( if you have this, remove it before installation of macOS Mojave ) • Samsung EVO Plus drives ( ensure you update Plus drive to latest firmware to avoid problems ) • XFX Radeon RX 580 • NVIDIA GTX / RTX not supported in macOS Mojave Q - WILL THIS GUIDE WORK WITH MY NON AORUS Z390 PRO MOTHERBOARD ? A - Possibly, though you may have to create your own USBPorts fix. Q - I notice you have the Aorus Pro Z390 version, will this guide work with Aorus Pro Z390 WiFi version ? A - Possibly, but onboard Intel / Intel CNVi WIFII /Bluetooth will not work with macOS and you will have to disable HS14 for Bluetooth to function properly. Q - Can I use my AMD Vega Card ? A - Yes, AMD Vega card's will work with this guide, but If you plan to use a Sapphire Pulse Vega 56 then please read @AudioGod ==>post regarding the Sapphire Pulse 56. PART 1 - DOWNLOAD • Update BIOS to version F10 • CLOVER • Aorus Pro Z390 EFI.zip • Aorus PRo Z390 EFI - THE OC VERSION.zip <== OC VERSION • ESP MOUNTER PRO v1.9 • macOS MOJAVE • CLOVER CONFIGURATOR • Hackintool OPTIONAL DOWNLOADS • Native Display Brightness with MonitorControl • ThemeEngine • Assets.car // Not really needed but IF no sound on Wake from Sleep then use SSDT-ALC1220 and CodecCommander • ( Resolves Audio Sound on Wake, place in Clover / ACPI / Patched ) • ( Resolves Audio Sound on Wake, place in Clover / Kexts / Other ) PART 2 - BIOS SETTINGS (Version F10 ) Here is a list of the BIOS settings that I use ( Screenshots in spoiler below ) • Enter BIOS → Press F12 → Enter Setup • Save & Exit → Load Optimized Defaults • BIOS → Windows 8/10 Features → Other OS • BIOS → CSM Support → Enabled ( Optionally, can be enabled after macOS is installed, your choice ) • Peripherals → Initial Display Output → PCIe 1 Slot • Peripherals → Trusted Computing → Security Device Support → Disable • Peripherals → Intel(R)Bios Guard → Intel BIOS Guard Support → Disable • Peripherals → USB Configuration → Legacy USB Support → Enabled • Peripherals → USB Configuration → XHCI Hand-off → Enabled • Peripherals → Network Stack Configuration → Network Stack → Disabled • Peripherals → SATA And RST Configuration → SATA Mode Selection → AHCI • Chipset → Vt-d → Enabled ( can be enabled or disabled, your choice!) • Chipset → Internal Graphics → Disabled • Chipset → Audio Controller → Enabled • Chipset → Above 4G Decoding → Disabled • Power → Platform Power Management → Disabled ( Optionally, can be enabled after macOS is installed ) • Power → CEC 2019 Ready → Disabled • Power → ErP → Disabled (can be enabled or disabled, your choice !) • Power → RC6 (Render Standby) → Disabled • MIT → Advanced Memory Settings → Extreme Memory Profile (X.M.P) → Disabled ( Optionally, can be enabled after macOS is installed, your choice ) // IF USING CORSAIR H100i V2 AIO CPU WATER COOLER • MIT → Smart Fan 5 Settings → CPU Fan Control mode → PWM • Save & Exit → Save & Exit Setup SCREEN DUMP SPOILERS PART 3 – CREATE A MOJAVE USB FLASH INSTALLER Prepare USB Installer for Mojave ( Video below ) • Insert USB drive • Launch /Applications/Utilities/Disk Utility • Disk Utility → View → Show All Devices • On Left-hand panel → External →(Identify your USB device in left hand panel) • Click and highlight your USB device in the left-hand panel. • Click erase button. • Name: USB • Format: Mac OS Extended (Journaled ) • Scheme: GUID Partition Map • Click Erase button. • Place the downloaded MacOS Mojave app into Applications folder. • Open Terminal copy and paste: sudo /Applications/Install\ macOS\ Mojave.app/Contents/Resources/createinstallmedia --volume /Volumes/USB --nointeraction && say Mojave Drive Created • Enter PART 4 – INSTALL CLOVER ON THE MOJAVE USB INSTALLER Make Mojave USB flash drive installer bootable.( Video below ) • Launch Clover application, double click. • Click Continue → Continue → Continue • Click Change Install Location button. • Click Install macOSMojave USB installer → Continue • Click Customise button • Choose: Clover for UEFI booting only Install Clover in the ESP Themes UEFI Drivers • Click Install button • Installation Complete! Video: PART 5 – CUSTOMIZE MOJAVE USB INSTALLER FOR AORUS Z390 PRO Replace Clover EFI folder with PRE-INSTALL Aorus Pro Z390 EFI - RX580.zip Aorus Pro Z390 EFI.zip ( Video below ) • Install ESP Mounter Pro v1.9 • Using ESP Mounter Pro, Mount ESP on disk2s1 ( Your disk name may be different ) • Open mounted EFI partition found on desktop • Copy all the contents from Aorus 390 Pro EFI folder • Replace USB EFI folder with all the contents inside the Aorus 390 Pro EFI folder. PART 6 – INSTALL MAC OS MOJAVE ON INTERNAL DRIVE INSTALL NOTE ENSURE BIOS: Above 4G Decoding is set to Disabled if Above 4G decoding is set to enabled then macOS Mojave install will freeze at 2 mins remaining and will not shut down properly!!!! Please be patient during install, so when install gets to 2 or 3 mins remaining then it may take extra time. Be ready to boot from UEFI USB installer by pressing F12 when install initiates restarts. • INSERT USB INSTALLER INTO THE USB 2.0 PORT Here is a walkthrough of the full process using the macOS Mojave USB Installer on the Aorus Z390 Pro. • Power on PC and press F12• Choose bootable USB drive from boot menu. • Install macOS Mojave to internal solid state or hard drive. When system returns to the Clover boot menu choose: • Boot macOS Install from Macintosh At next restart, press F12 and boot from external UEFI USB device and choose: • Boot macOS Install from Macintosh Proceed with macOS Mojave install macOS Mojave is now installed, but it can only boot at this moment thanks to FakeSMC and Clover on the Mojave USB flash drive installer. PART 7 – MAKE AORUS Z390 PRO INTERNAL DRIVE BOOTABLE Make internal drive bootable ( Video below ) So far, the Aorus Pro can only boot the internal system drive with the aid of the Mojave USB Installer. To boot from the internal system drive without the installer: Download and install Clover with RC Scripts on target volume. Copy the EFI folder from inside Aorus Pro Z390 EFI.zip folder and paste it inside the the System Drive EFI partition. • Remove USB Mojave installer and shut down and restart. Aorus Hackintosh should now be able to boot to macOS Mojave, Done, well almost ! PART 8 – ENABLE IMESSAGES & FACETIME // UPDATE 21st MAY 2019 Possibly Clover Configurator now automatically populates correct values for working iMessages when you select an SMBIOS. After selecting SMBIOS, example iMac19,1 for Aorus Pro with RX580 ( image above ) then go to Apple and ensure you have the "serial number is not valid " message. Done! If you still have problems connecting to iMessage, test and ensure that AirDrop is working, then follow instructions inside spoiler. PART 9 – ENABLE TRIM for Solid State Flash Drives Open Terminal and enter the following command: sudo trimforce enable PART 10 – FRAMEBUFFERS FOR RADEON AMD RX580, VEGA CARD's DEFAULT USB FIX – USB PORTS CONFIGURATION If you have USBC on Computer Chassis / Case, then SS01 and SS02 is mapped to that USB C port ------------ GUIDE FINISHED YOU SHOULD NOW HAVE WORKING AORUS Z390 PRO HACKINTOSH WITH SSDT USB FIX ------------ OPTIONAL: Set Wi-Fi Country Code OPTIONAL: System Information - PCI External USB Storage: Fix "disk did not eject properly" message upon wake from sleep OPTIONAL: Native Display Brightness - with MonitorControl OPTIONAL: Dual Boot macOS Mojave & Windows 10 OPTIONAL: Replace the default "About This Mac" Apple Logo with RED AORUS APPLE OPTIONAL USB PORTS FIX – Create your own SSDT or USBPorts.kext FRAMEBUFFER PATCHING – For working Intel UHD 630 Graphics, working HDMI Port, working HDMI Audio on Aorus Z390 Pro NOT REQUIRED AS GUIDE IS USING SMBIOS FOR IMAC PRO 1,1 FINAL CUT PRO – Configuration for AMD RX5xx NOT REQUIRED AS GUIDE IS USING SMBIOS FOR IMAC PRO 1,1 AORUS PRO Z390 WIFI version with Intel CNVi – Disable Bluetooth on HS14 Resolve bluetooth issue reported by @eSaF CLOVER – Updating / Upgrade Clover boot loader (If hack is stable, don't update unless you have problems) SLEEP – Sleep and Automatic Sleep SLEEP – Resolving Instant Wake ( Corsair H100i v2 AIO ) WIFI – Clover Hotpatch PXSX to ARPT RECOMMENDED READING – Excellent Hackintosh Vanilla guide created by CorpNewt with in depth tutorial on Clover. https://hackintosh.gitbook.io/-r-hackintosh-vanilla-desktop-guide/config.plist-per-hardware/coffee-lake EFI NON DSDT SMBIOS iMac Pro 1,1 Clover v2.5k r5018 Aorus Pro Z390 EFI - RX580.zip OR Aorus Pro Z390 EFI - Vega-56.zip EFI FOR SMBIOS iMac 19,1 for use with GPU & IGPU enabled in BIOS PRE-INSTALL Aorus Pro Z390 EFI - RX580.zip POST-INSTALL Aorus Pro Z390 EFI - RX580.zip ( Has OsxAptioFix2Drv-free2000.efi ==> recommended reading before use ) EFI FOR INTEL UHD 630 SMBIOS iMAC 18,1 Aorus Pro Z390 EFI - Intel UHD630.zip( Has OsxAptioFix2Drv-free2000.efi ==> recommended reading before use )1 point

-

The AirPortAtheros40.kext as similiar code found on linux freebsd. This first patch was tested on OS X 10.11.0 Working card: Qualcomm Atheros AR9565 pci168c,36 with bluetooth Download v01 for 0036 card + BTFirmwareUploader in attachments. Post your questions here You can find updates on EMlyDinEsH BTFirmwareUploader here http://forum.osxlatitude.com/index.php?/topic/2925-bluetooth-firmware-uploader/ v01 also works on 10.11.4 TOFIX: Bands/Channels limitation exist in macosx/windows driver but not in linux UPDATE: v03 fixed eprom local check. This kext check the following mac models. This might disable/enable some features. plz check your smbios mac model. I'm not using any of this models in my smbios v21 = 31; if ( PEGetModelName(&v40, 32LL) ) { v22 = !strcmp(&v40, "iMac10,1") || !strcmp(&v40, "iMac11,1") || !strcmp(&v40, "iMac11,2") || !strcmp(&v40, "MacBookPro5,2"); if ( !strcmp(&v40, "iMac12,1") || !strcmp(&v40, "iMac12,2") ) v21 = 29; } else { v22 = 0; } DEV NOTES: The driver attach procedure loads one of 2 main subs: ar5416Attach(); ar9300Attach(); On the 9300 tree we have native support for #define AR_SREV_VERSION_OSPREY 0x1C0 #define AR_SREV_VERSION_AR9580 0x1C0 #define AR_SREV_VERSION_HORNET 0x200 The 0036 card is set here #define AR_SREV_VERSION_APHRODITE 0x2C0 For other cards check here ath_hal_mac_name(struct ath_hal *ah) 90 { 91 switch (ah->ah_macVersion) { 92 case AR_SREV_VERSION_CRETE: 93 case AR_SREV_VERSION_MAUI_1: 94 return "AR5210"; 95 case AR_SREV_VERSION_MAUI_2: 96 case AR_SREV_VERSION_OAHU: 97 return "AR5211"; 98 case AR_SREV_VERSION_VENICE: 99 return "AR5212"; 100 case AR_SREV_VERSION_GRIFFIN: 101 return "AR2413"; 102 case AR_SREV_VERSION_CONDOR: 103 return "AR5424"; 104 case AR_SREV_VERSION_EAGLE: 105 return "AR5413"; 106 case AR_SREV_VERSION_COBRA: 107 return "AR2415"; 108 case AR_SREV_2425: /* Swan */ 109 return "AR2425"; 110 case AR_SREV_2417: /* Nala */ 111 return "AR2417"; 112 case AR_XSREV_VERSION_OWL_PCI: 113 return "AR5416"; 114 case AR_XSREV_VERSION_OWL_PCIE: 115 return "AR5418"; 116 case AR_XSREV_VERSION_HOWL: 117 return "AR9130"; 118 case AR_XSREV_VERSION_SOWL: 119 return "AR9160"; 120 case AR_XSREV_VERSION_MERLIN: 121 if (AH_PRIVATE(ah)->ah_ispcie) 122 return "AR9280"; 123 return "AR9220"; 124 case AR_XSREV_VERSION_KITE: 125 return "AR9285"; 126 case AR_XSREV_VERSION_KIWI: 127 if (AH_PRIVATE(ah)->ah_ispcie) 128 return "AR9287"; 129 return "AR9227"; 130 case AR_SREV_VERSION_AR9380: 131 if (ah->ah_macRev >= AR_SREV_REVISION_AR9580_10) 132 return "AR9580"; 133 return "AR9380"; 134 case AR_SREV_VERSION_AR9460: 135 return "AR9460"; 136 case AR_SREV_VERSION_AR9330: 137 return "AR9330"; 138 case AR_SREV_VERSION_AR9340: 139 return "AR9340"; 140 case AR_SREV_VERSION_QCA9550: 141 return "QCA9550"; 142 case AR_SREV_VERSION_AR9485: 143 return "AR9485"; 144 case AR_SREV_VERSION_QCA9565: 145 return "QCA9565"; 146 case AR_SREV_VERSION_QCA9530: 147 return "QCA9530"; 148 } 149 return "????"; 150 } A reference to freebsd source code (usefull to in code research for other cards): http://code.metager.de/source/xref/freebsd/sys/contrib/dev/ath/ath_hal/ar9300/ And ofc the linux id search engine: http://lxr.free-electrons.com/ident apple code is very old but still some patches can be done Todo: Test domains references: static REG_DMN_PAIR_MAPPING regDomainPairs[] = { 32 {NO_ENUMRD, DEBUG_REG_DMN, DEBUG_REG_DMN, NO_REQ, NO_REQ, PSCAN_DEFER, CTRY_DEFAULT }, 33 {NULL1_WORLD, NULL1, WORLD, NO_REQ, NO_REQ, PSCAN_DEFER, CTRY_DEFAULT }, 34 {NULL1_ETSIB, NULL1, ETSIB, NO_REQ, NO_REQ, PSCAN_DEFER, CTRY_DEFAULT }, 35 {NULL1_ETSIC, NULL1, ETSIC, NO_REQ, NO_REQ, PSCAN_DEFER, CTRY_DEFAULT }, 36 37 {FCC2_FCCA, FCC2, FCCA, NO_REQ, NO_REQ, PSCAN_DEFER, CTRY_DEFAULT }, 38 {FCC2_WORLD, FCC2, WORLD, NO_REQ, NO_REQ, PSCAN_DEFER, CTRY_DEFAULT }, 39 {FCC2_ETSIC, FCC2, ETSIC, NO_REQ, NO_REQ, PSCAN_DEFER, CTRY_DEFAULT }, 40 {FCC3_FCCA, FCC3, FCCA, NO_REQ, NO_REQ, PSCAN_DEFER, CTRY_DEFAULT }, 41 {FCC3_WORLD, FCC3, WORLD, NO_REQ, NO_REQ, PSCAN_DEFER, CTRY_DEFAULT }, 42 {FCC4_FCCA, FCC4, FCCA, DISALLOW_ADHOC_11A | DISALLOW_ADHOC_11A_TURB, NO_REQ, PSCAN_DEFER, CTRY_DEFAULT }, 43 {FCC5_FCCB, FCC5, FCCB, NO_REQ, NO_REQ, PSCAN_DEFER, CTRY_DEFAULT }, 44 45 {ETSI1_WORLD, ETSI1, WORLD, DISALLOW_ADHOC_11A | DISALLOW_ADHOC_11A_TURB, NO_REQ, PSCAN_DEFER, CTRY_DEFAULT }, 46 {ETSI2_WORLD, ETSI2, WORLD, DISALLOW_ADHOC_11A | DISALLOW_ADHOC_11A_TURB, NO_REQ, PSCAN_DEFER, CTRY_DEFAULT }, 47 {ETSI3_WORLD, ETSI3, WORLD, DISALLOW_ADHOC_11A | DISALLOW_ADHOC_11A_TURB, NO_REQ, PSCAN_DEFER, CTRY_DEFAULT }, 48 {ETSI4_WORLD, ETSI4, WORLD, DISALLOW_ADHOC_11A | DISALLOW_ADHOC_11A_TURB, NO_REQ, PSCAN_DEFER, CTRY_DEFAULT }, 49 {ETSI5_WORLD, ETSI5, WORLD, DISALLOW_ADHOC_11A | DISALLOW_ADHOC_11A_TURB, NO_REQ, PSCAN_DEFER, CTRY_DEFAULT }, 50 {ETSI6_WORLD, ETSI6, WORLD, DISALLOW_ADHOC_11A | DISALLOW_ADHOC_11A_TURB, NO_REQ, PSCAN_DEFER, CTRY_DEFAULT }, 51 52 {ETSI3_ETSIA, ETSI3, WORLD, DISALLOW_ADHOC_11A | DISALLOW_ADHOC_11A_TURB, NO_REQ, PSCAN_DEFER, CTRY_DEFAULT }, 53 {FRANCE_RES, ETSI3, WORLD, NO_REQ, NO_REQ, PSCAN_DEFER, CTRY_DEFAULT }, 54 55 {FCC1_WORLD, FCC1, WORLD, NO_REQ, NO_REQ, PSCAN_DEFER, CTRY_DEFAULT }, 56 {FCC1_FCCA, FCC1, FCCA, NO_REQ, NO_REQ, PSCAN_DEFER, CTRY_DEFAULT }, 57 {APL1_WORLD, APL1, WORLD, NO_REQ, NO_REQ, PSCAN_DEFER, CTRY_DEFAULT }, 58 {APL2_WORLD, APL2, WORLD, NO_REQ, NO_REQ, PSCAN_DEFER, CTRY_DEFAULT }, 59 {APL3_WORLD, APL3, WORLD, NO_REQ, NO_REQ, PSCAN_DEFER, CTRY_DEFAULT }, 60 {APL4_WORLD, APL4, WORLD, NO_REQ, NO_REQ, PSCAN_DEFER, CTRY_DEFAULT }, 61 {APL5_WORLD, APL5, WORLD, NO_REQ, NO_REQ, PSCAN_DEFER, CTRY_DEFAULT }, 62 {APL6_WORLD, APL6, WORLD, NO_REQ, NO_REQ, PSCAN_DEFER, CTRY_DEFAULT }, 63 {APL8_WORLD, APL8, WORLD, NO_REQ, NO_REQ, PSCAN_DEFER, CTRY_DEFAULT }, 64 {APL9_WORLD, APL9, WORLD, NO_REQ, NO_REQ, PSCAN_DEFER, CTRY_DEFAULT }, 65 66 {APL3_FCCA, APL3, FCCA, NO_REQ, NO_REQ, PSCAN_DEFER, CTRY_DEFAULT }, 67 {APL1_ETSIC, APL1, ETSIC, NO_REQ, NO_REQ, PSCAN_DEFER, CTRY_DEFAULT }, 68 {APL2_ETSIC, APL2, ETSIC, NO_REQ, NO_REQ, PSCAN_DEFER, CTRY_DEFAULT }, 69 {APL2_APLD, APL2, APLD, NO_REQ, NO_REQ, PSCAN_DEFER, CTRY_DEFAULT }, 70 71 {MKK1_MKKA, MKK1, MKKA, DISALLOW_ADHOC_11A_TURB | NEED_NFC | LIMIT_FRAME_4MS, NEED_NFC, PSCAN_MKK1 | PSCAN_MKKA, CTRY_JAPAN }, 72 {MKK1_MKKB, MKK1, MKKA, DISALLOW_ADHOC_11A | DISALLOW_ADHOC_11A_TURB | NEED_NFC| LIMIT_FRAME_4MS, NEED_NFC, PSCAN_MKK1 | PSCAN_MKKA | PSCAN_MKKA_G, CTRY_JAPAN1 }, 73 {MKK1_FCCA, MKK1, FCCA, DISALLOW_ADHOC_11A_TURB | NEED_NFC| LIMIT_FRAME_4MS, NEED_NFC, PSCAN_MKK1, CTRY_JAPAN2 }, 74 {MKK1_MKKA1, MKK1, MKKA, DISALLOW_ADHOC_11A_TURB | NEED_NFC| LIMIT_FRAME_4MS, NEED_NFC, PSCAN_MKK1 | PSCAN_MKKA1 | PSCAN_MKKA1_G, CTRY_JAPAN4 }, 75 {MKK1_MKKA2, MKK1, MKKA, DISALLOW_ADHOC_11A_TURB | NEED_NFC| LIMIT_FRAME_4MS, NEED_NFC, PSCAN_MKK1 | PSCAN_MKKA2 | PSCAN_MKKA2_G, CTRY_JAPAN5 }, 76 {MKK1_MKKC, MKK1, MKKC, DISALLOW_ADHOC_11A_TURB | NEED_NFC| LIMIT_FRAME_4MS, NEED_NFC, PSCAN_MKK1, CTRY_JAPAN6 }, 77 78 /* MKK2 */ 79 {MKK2_MKKA, MKK2, MKKA, DISALLOW_ADHOC_11A | DISALLOW_ADHOC_11A_TURB | NEED_NFC| LIMIT_FRAME_4MS, NEED_NFC, PSCAN_MKK2 | PSCAN_MKKA | PSCAN_MKKA_G, CTRY_JAPAN3 }, 80 81 /* MKK3 */ 82 {MKK3_MKKA, MKK3, MKKA, DISALLOW_ADHOC_11A_TURB | NEED_NFC | LIMIT_FRAME_4MS, NEED_NFC , PSCAN_MKKA, CTRY_DEFAULT }, 83 {MKK3_MKKB, MKK3, MKKA, DISALLOW_ADHOC_11A | DISALLOW_ADHOC_11A_TURB | NEED_NFC | LIMIT_FRAME_4MS, NEED_NFC, PSCAN_MKKA | PSCAN_MKKA_G, CTRY_JAPAN7 }, 84 {MKK3_MKKA1, MKK3, MKKA, DISALLOW_ADHOC_11A_TURB | NEED_NFC | LIMIT_FRAME_4MS, NEED_NFC, PSCAN_MKKA1 | PSCAN_MKKA1_G, CTRY_DEFAULT }, 85 {MKK3_MKKA2,MKK3, MKKA, DISALLOW_ADHOC_11A_TURB | NEED_NFC | LIMIT_FRAME_4MS, NEED_NFC, PSCAN_MKKA2 | PSCAN_MKKA2_G, CTRY_JAPAN8 }, 86 {MKK3_MKKC, MKK3, MKKC, DISALLOW_ADHOC_11A_TURB | NEED_NFC | LIMIT_FRAME_4MS, NEED_NFC, NO_PSCAN, CTRY_JAPAN9 }, 87 {MKK3_FCCA, MKK3, FCCA, DISALLOW_ADHOC_11A_TURB | NEED_NFC | LIMIT_FRAME_4MS, NEED_NFC, NO_PSCAN, CTRY_DEFAULT }, 88 89 /* MKK4 */ 90 {MKK4_MKKB, MKK4, MKKA, DISALLOW_ADHOC_11A | DISALLOW_ADHOC_11A_TURB | NEED_NFC | LIMIT_FRAME_4MS, NEED_NFC, PSCAN_MKK3 | PSCAN_MKKA | PSCAN_MKKA_G, CTRY_JAPAN10 }, 91 {MKK4_MKKA1, MKK4, MKKA, DISALLOW_ADHOC_11A_TURB | NEED_NFC | LIMIT_FRAME_4MS, NEED_NFC, PSCAN_MKK3 | PSCAN_MKKA1 | PSCAN_MKKA1_G, CTRY_DEFAULT }, 92 {MKK4_MKKA2, MKK4, MKKA, DISALLOW_ADHOC_11A_TURB | NEED_NFC | LIMIT_FRAME_4MS, NEED_NFC, PSCAN_MKK3 |PSCAN_MKKA2 | PSCAN_MKKA2_G, CTRY_JAPAN11 }, 93 {MKK4_MKKC, MKK4, MKKC, DISALLOW_ADHOC_11A_TURB | NEED_NFC | LIMIT_FRAME_4MS, NEED_NFC, PSCAN_MKK3, CTRY_JAPAN12 }, 94 {MKK4_FCCA, MKK4, FCCA, DISALLOW_ADHOC_11A_TURB | NEED_NFC | LIMIT_FRAME_4MS, NEED_NFC, PSCAN_MKK3, CTRY_DEFAULT }, 95 96 /* MKK5 */ 97 {MKK5_MKKB, MKK5, MKKA, DISALLOW_ADHOC_11A | DISALLOW_ADHOC_11A_TURB | NEED_NFC | LIMIT_FRAME_4MS, NEED_NFC, PSCAN_MKK3 | PSCAN_MKKA | PSCAN_MKKA_G, CTRY_JAPAN13 }, 98 {MKK5_MKKA2,MKK5, MKKA, DISALLOW_ADHOC_11A_TURB | NEED_NFC | LIMIT_FRAME_4MS, NEED_NFC, PSCAN_MKK3 | PSCAN_MKKA2 | PSCAN_MKKA2_G, CTRY_JAPAN14 }, 99 {MKK5_MKKC, MKK5, MKKC, DISALLOW_ADHOC_11A_TURB | NEED_NFC | LIMIT_FRAME_4MS, NEED_NFC, PSCAN_MKK3, CTRY_JAPAN15 }, 100 101 /* MKK6 */ 102 {MKK6_MKKB, MKK6, MKKA, DISALLOW_ADHOC_11A | DISALLOW_ADHOC_11A_TURB | NEED_NFC | LIMIT_FRAME_4MS, NEED_NFC, PSCAN_MKK1 | PSCAN_MKKA | PSCAN_MKKA_G, CTRY_JAPAN16 }, 103 {MKK6_MKKA2, MKK6, MKKA, DISALLOW_ADHOC_11A_TURB | NEED_NFC | LIMIT_FRAME_4MS, NEED_NFC, PSCAN_MKK1 | PSCAN_MKKA2 | PSCAN_MKKA2_G, CTRY_JAPAN17 }, 104 {MKK6_MKKC, MKK6, MKKC, DISALLOW_ADHOC_11A_TURB | NEED_NFC | LIMIT_FRAME_4MS, NEED_NFC, PSCAN_MKK1, CTRY_JAPAN18 }, 105 106 /* MKK7 */ 107 {MKK7_MKKB, MKK7, MKKA, DISALLOW_ADHOC_11A | DISALLOW_ADHOC_11A_TURB | NEED_NFC | LIMIT_FRAME_4MS, NEED_NFC, PSCAN_MKK1 | PSCAN_MKK3 | PSCAN_MKKA | PSCAN_MKKA_G, CTRY_JAPAN19 }, 108 {MKK7_MKKA2, MKK7, MKKA, DISALLOW_ADHOC_11A_TURB | NEED_NFC | LIMIT_FRAME_4MS, NEED_NFC, PSCAN_MKK1 | PSCAN_MKK3 | PSCAN_MKKA2 | PSCAN_MKKA2_G, CTRY_JAPAN20 }, 109 {MKK7_MKKC, MKK7, MKKC, DISALLOW_ADHOC_11A_TURB | NEED_NFC | LIMIT_FRAME_4MS, NEED_NFC, PSCAN_MKK1 | PSCAN_MKK3, CTRY_JAPAN21 }, 110 111 /* MKK8 */ 112 {MKK8_MKKB, MKK8, MKKA, DISALLOW_ADHOC_11A | DISALLOW_ADHOC_11A_TURB | NEED_NFC | LIMIT_FRAME_4MS, NEED_NFC, PSCAN_MKK1 | PSCAN_MKK3 | PSCAN_MKKA | PSCAN_MKKA_G, CTRY_JAPAN22 }, 113 {MKK8_MKKA2,MKK8, MKKA, DISALLOW_ADHOC_11A_TURB | NEED_NFC | LIMIT_FRAME_4MS, NEED_NFC, PSCAN_MKK1 | PSCAN_MKK3 | PSCAN_MKKA2 | PSCAN_MKKA2_G, CTRY_JAPAN23 }, 114 {MKK8_MKKC, MKK8, MKKC, DISALLOW_ADHOC_11A_TURB | NEED_NFC | LIMIT_FRAME_4MS, NEED_NFC, PSCAN_MKK1 | PSCAN_MKK3 , CTRY_JAPAN24 }, 115 116 {MKK9_MKKA, MKK9, MKKA, DISALLOW_ADHOC_11A | DISALLOW_ADHOC_11A_TURB | NEED_NFC | LIMIT_FRAME_4MS, NEED_NFC, PSCAN_MKK3 | PSCAN_MKKA | PSCAN_MKKA_G, CTRY_DEFAULT }, 117 {MKK10_MKKA, MKK10, MKKA, DISALLOW_ADHOC_11A | DISALLOW_ADHOC_11A_TURB | NEED_NFC | LIMIT_FRAME_4MS, NEED_NFC, PSCAN_MKK3 | PSCAN_MKKA | PSCAN_MKKA_G, CTRY_DEFAULT }, 118 119 /* These are super domains */ 120 {WOR0_WORLD, WOR0_WORLD, WOR0_WORLD, NO_REQ, NO_REQ, PSCAN_DEFER, CTRY_DEFAULT }, 121 {WOR1_WORLD, WOR1_WORLD, WOR1_WORLD, DISALLOW_ADHOC_11A | DISALLOW_ADHOC_11A_TURB, NO_REQ, PSCAN_DEFER, CTRY_DEFAULT }, 122 {WOR2_WORLD, WOR2_WORLD, WOR2_WORLD, DISALLOW_ADHOC_11A_TURB, NO_REQ, PSCAN_DEFER, CTRY_DEFAULT }, 123 {WOR3_WORLD, WOR3_WORLD, WOR3_WORLD, NO_REQ, NO_REQ, PSCAN_DEFER, CTRY_DEFAULT }, 124 {WOR4_WORLD, WOR4_WORLD, WOR4_WORLD, DISALLOW_ADHOC_11A | DISALLOW_ADHOC_11A_TURB, NO_REQ, PSCAN_DEFER, CTRY_DEFAULT }, 125 {WOR5_ETSIC, WOR5_ETSIC, WOR5_ETSIC, DISALLOW_ADHOC_11A | DISALLOW_ADHOC_11A_TURB, NO_REQ, PSCAN_DEFER, CTRY_DEFAULT }, 126 {WOR01_WORLD, WOR01_WORLD, WOR01_WORLD, NO_REQ, NO_REQ, PSCAN_DEFER, CTRY_DEFAULT }, 127 {WOR02_WORLD, WOR02_WORLD, WOR02_WORLD, NO_REQ, NO_REQ, PSCAN_DEFER, CTRY_DEFAULT }, 128 {EU1_WORLD, EU1_WORLD, EU1_WORLD, NO_REQ, NO_REQ, PSCAN_DEFER, CTRY_DEFAULT }, 129 {WOR9_WORLD, WOR9_WORLD, WOR9_WORLD, DISALLOW_ADHOC_11A | DISALLOW_ADHOC_11A_TURB, NO_REQ, PSCAN_DEFER, CTRY_DEFAULT }, 130 {WORA_WORLD, WORA_WORLD, WORA_WORLD, DISALLOW_ADHOC_11A | DISALLOW_ADHOC_11A_TURB, NO_REQ, PSCAN_DEFER, CTRY_DEFAULT }, 131 {WORB_WORLD, WORB_WORLD, WORB_WORLD, DISALLOW_ADHOC_11A | DISALLOW_ADHOC_11A_TURB, NO_REQ, PSCAN_DEFER, CTRY_DEFAULT }, 132 {WORC_WORLD, WORC_WORLD, WORC_WORLD, NO_REQ, NO_REQ, PSCAN_DEFER, CTRY_DEFAULT }, 133}; and the ids: enum { 31 /* 32 * The following regulatory domain definitions are 33 * found in the EEPROM. Each regulatory domain 34 * can operate in either a 5GHz or 2.4GHz wireless mode or 35 * both 5GHz and 2.4GHz wireless modes. 36 * In general, the value holds no special 37 * meaning and is used to decode into either specific 38 * 2.4GHz or 5GHz wireless mode for that particular 39 * regulatory domain. 40 */ 41 NO_ENUMRD = 0x00, 42 NULL1_WORLD = 0x03, /* For 11b-only countries (no 11a allowed) */ 43 NULL1_ETSIB = 0x07, /* Israel */ 44 NULL1_ETSIC = 0x08, 45 FCC1_FCCA = 0x10, /* USA */ 46 FCC1_WORLD = 0x11, /* Hong Kong */ 47 FCC4_FCCA = 0x12, /* USA - Public Safety */ 48 FCC5_FCCB = 0x13, /* USA w/ 1/2 and 1/4 width channels */ 49 FCC6_FCCA = 0x14, /* Canada for AP only */ 50 51 FCC2_FCCA = 0x20, /* Canada */ 52 FCC2_WORLD = 0x21, /* Australia & HK */ 53 FCC2_ETSIC = 0x22, 54 FCC_UBNT = 0x2A, /* Ubiquity PicoStation M2HP */ 55 FRANCE_RES = 0x31, /* Legacy France for OEM */ 56 FCC3_FCCA = 0x3A, /* USA & Canada w/5470 band, 11h, DFS enabled */ 57 FCC3_WORLD = 0x3B, /* USA & Canada w/5470 band, 11h, DFS enabled */ 58 59 ETSI1_WORLD = 0x37, 60 ETSI3_ETSIA = 0x32, /* France (optional) */ 61 ETSI2_WORLD = 0x35, /* Hungary & others */ 62 ETSI3_WORLD = 0x36, /* France & others */ 63 ETSI4_WORLD = 0x30, 64 ETSI4_ETSIC = 0x38, 65 ETSI5_WORLD = 0x39, 66 ETSI6_WORLD = 0x34, /* Bulgaria */ 67 ETSI8_WORLD = 0x3D, /* Russia */ 68 ETSI9_WORLD = 0x3E, /* Ukraine */ 69 ETSI_RESERVED = 0x33, /* Reserved (Do not used) */ 70 71 MKK1_MKKA = 0x40, /* Japan (JP1) */ 72 MKK1_MKKB = 0x41, /* Japan (JP0) */ 73 APL4_WORLD = 0x42, /* Singapore */ 74 MKK2_MKKA = 0x43, /* Japan with 4.9G channels */ 75 APL_RESERVED = 0x44, /* Reserved (Do not used) */ 76 APL2_WORLD = 0x45, /* Korea */ 77 APL2_APLC = 0x46, 78 APL3_WORLD = 0x47, 79 MKK1_FCCA = 0x48, /* Japan (JP1-1) */ 80 APL2_APLD = 0x49, /* Korea with 2.3G channels */ 81 MKK1_MKKA1 = 0x4A, /* Japan (JE1) */ 82 MKK1_MKKA2 = 0x4B, /* Japan (JE2) */ 83 MKK1_MKKC = 0x4C, /* Japan (MKK1_MKKA,except Ch14) */ 84 APL2_FCCA = 0x4D, /* Mobile customer */ 85 86 APL3_FCCA = 0x50, 87 APL1_WORLD = 0x52, /* Latin America */ 88 APL1_FCCA = 0x53, 89 APL1_APLA = 0x54, 90 APL1_ETSIC = 0x55, 91 APL2_ETSIC = 0x56, /* Venezuela */ 92 APL5_WORLD = 0x58, /* Chile */ 93 APL6_WORLD = 0x5B, /* Singapore */ 94 APL7_FCCA = 0x5C, /* Taiwan 5.47 Band */ 95 APL8_WORLD = 0x5D, /* Malaysia 5GHz */ 96 APL9_WORLD = 0x5E, /* Korea 5GHz; before 11/2007; now APs only */ 97 APL10_WORLD = 0x5F, /* Korea 5GHz; After 11/2007; STAs only */ 98 99 /* 100 * World mode SKUs 101 */ 102 WOR0_WORLD = 0x60, /* World0 (WO0 SKU) */ 103 WOR1_WORLD = 0x61, /* World1 (WO1 SKU) */ 104 WOR2_WORLD = 0x62, /* World2 (WO2 SKU) */ 105 WOR3_WORLD = 0x63, /* World3 (WO3 SKU) */ 106 WOR4_WORLD = 0x64, /* World4 (WO4 SKU) */ 107 WOR5_ETSIC = 0x65, /* World5 (WO5 SKU) */ 108 109 WOR01_WORLD = 0x66, /* World0-1 (WW0-1 SKU) */ 110 WOR02_WORLD = 0x67, /* World0-2 (WW0-2 SKU) */ 111 EU1_WORLD = 0x68, /* Same as World0-2 (WW0-2 SKU), except active scan ch1-13. No ch14 */ 112 113 WOR9_WORLD = 0x69, /* World9 (WO9 SKU) */ 114 WORA_WORLD = 0x6A, /* WorldA (WOA SKU) */ 115 WORB_WORLD = 0x6B, /* WorldB (WOB SKU) */ 116 WORC_WORLD = 0x6C, /* WorldC (WOC SKU) */ 117 118 MKK3_MKKB = 0x80, /* Japan UNI-1 even + MKKB */ 119 MKK3_MKKA2 = 0x81, /* Japan UNI-1 even + MKKA2 */ 120 MKK3_MKKC = 0x82, /* Japan UNI-1 even + MKKC */ 121 122 MKK4_MKKB = 0x83, /* Japan UNI-1 even + UNI-2 + MKKB */ 123 MKK4_MKKA2 = 0x84, /* Japan UNI-1 even + UNI-2 + MKKA2 */ 124 MKK4_MKKC = 0x85, /* Japan UNI-1 even + UNI-2 + MKKC */ 125 126 MKK5_MKKB = 0x86, /* Japan UNI-1 even + UNI-2 + mid-band + MKKB */ 127 MKK5_MKKA2 = 0x87, /* Japan UNI-1 even + UNI-2 + mid-band + MKKA2 */ 128 MKK5_MKKC = 0x88, /* Japan UNI-1 even + UNI-2 + mid-band + MKKC */ 129 130 MKK6_MKKB = 0x89, /* Japan UNI-1 even + UNI-1 odd MKKB */ 131 MKK6_MKKA2 = 0x8A, /* Japan UNI-1 even + UNI-1 odd + MKKA2 */ 132 MKK6_MKKC = 0x8B, /* Japan UNI-1 even + UNI-1 odd + MKKC */ 133 134 MKK7_MKKB = 0x8C, /* Japan UNI-1 even + UNI-1 odd + UNI-2 + MKKB */ 135 MKK7_MKKA2 = 0x8D, /* Japan UNI-1 even + UNI-1 odd + UNI-2 + MKKA2 */ 136 MKK7_MKKC = 0x8E, /* Japan UNI-1 even + UNI-1 odd + UNI-2 + MKKC */ 137 138 MKK8_MKKB = 0x8F, /* Japan UNI-1 even + UNI-1 odd + UNI-2 + mid-band + MKKB */ 139 MKK8_MKKA2 = 0x90, /* Japan UNI-1 even + UNI-1 odd + UNI-2 + mid-band + MKKA2 */ 140 MKK8_MKKC = 0x91, /* Japan UNI-1 even + UNI-1 odd + UNI-2 + mid-band + MKKC */ 141 142 MKK14_MKKA1 = 0x92, /* Japan UNI-1 even + UNI-1 odd + 4.9GHz + MKKA1 */ 143 MKK15_MKKA1 = 0x93, /* Japan UNI-1 even + UNI-1 odd + UNI-2 + 4.9GHz + MKKA1 */ 144 145 MKK10_FCCA = 0xD0, /* Japan UNI-1 even + UNI-2 + 4.9GHz + FCCA */ 146 MKK10_MKKA1 = 0xD1, /* Japan UNI-1 even + UNI-2 + 4.9GHz + MKKA1 */ 147 MKK10_MKKC = 0xD2, /* Japan UNI-1 even + UNI-2 + 4.9GHz + MKKC */ 148 MKK10_MKKA2 = 0xD3, /* Japan UNI-1 even + UNI-2 + 4.9GHz + MKKA2 */ 149 150 MKK11_MKKA = 0xD4, /* Japan UNI-1 even + UNI-2 + mid-band + 4.9GHz + MKKA */ 151 MKK11_FCCA = 0xD5, /* Japan UNI-1 even + UNI-2 + mid-band + 4.9GHz + FCCA */ 152 MKK11_MKKA1 = 0xD6, /* Japan UNI-1 even + UNI-2 + mid-band + 4.9GHz + MKKA1 */ 153 MKK11_MKKC = 0xD7, /* Japan UNI-1 even + UNI-2 + mid-band + 4.9GHz + MKKC */ 154 MKK11_MKKA2 = 0xD8, /* Japan UNI-1 even + UNI-2 + mid-band + 4.9GHz + MKKA2 */ 155 156 MKK12_MKKA = 0xD9, /* Japan UNI-1 even + UNI-1 odd + UNI-2 + mid-band + 4.9GHz + MKKA */ 157 MKK12_FCCA = 0xDA, /* Japan UNI-1 even + UNI-1 odd + UNI-2 + mid-band + 4.9GHz + FCCA */ 158 MKK12_MKKA1 = 0xDB, /* Japan UNI-1 even + UNI-1 odd + UNI-2 + mid-band + 4.9GHz + MKKA1 */ 159 MKK12_MKKC = 0xDC, /* Japan UNI-1 even + UNI-1 odd + UNI-2 + mid-band + 4.9GHz + MKKC */ 160 MKK12_MKKA2 = 0xDD, /* Japan UNI-1 even + UNI-1 odd + UNI-2 + mid-band + 4.9GHz + MKKA2 */ 161 162 MKK13_MKKB = 0xDE, /* Japan UNI-1 even + UNI-1 odd + UNI-2 + mid-band + MKKB + All passive + no adhoc */ 163 164 /* 165 * Following definitions are used only by s/w to map old 166 * Japan SKUs. 167 */ 168 MKK3_MKKA = 0xF0, /* Japan UNI-1 even + MKKA */ 169 MKK3_MKKA1 = 0xF1, /* Japan UNI-1 even + MKKA1 */ 170 MKK3_FCCA = 0xF2, /* Japan UNI-1 even + FCCA */ 171 MKK4_MKKA = 0xF3, /* Japan UNI-1 even + UNI-2 + MKKA */ 172 MKK4_MKKA1 = 0xF4, /* Japan UNI-1 even + UNI-2 + MKKA1 */ 173 MKK4_FCCA = 0xF5, /* Japan UNI-1 even + UNI-2 + FCCA */ 174 MKK9_MKKA = 0xF6, /* Japan UNI-1 even + 4.9GHz */ 175 MKK10_MKKA = 0xF7, /* Japan UNI-1 even + UNI-2 + 4.9GHz */ 176 MKK6_MKKA1 = 0xF8, /* Japan UNI-1 even + UNI-1 odd + UNI-2 + MKKA1 */ 177 MKK6_FCCA = 0xF9, /* Japan UNI-1 even + UNI-1 odd + UNI-2 + FCCA */ 178 MKK7_MKKA1 = 0xFA, /* Japan UNI-1 even + UNI-1 odd + UNI-2 + MKKA1 */ 179 MKK7_FCCA = 0xFB, /* Japan UNI-1 even + UNI-1 odd + UNI-2 + FCCA */ 180 MKK9_FCCA = 0xFC, /* Japan UNI-1 even + 4.9GHz + FCCA */ 181 MKK9_MKKA1 = 0xFD, /* Japan UNI-1 even + 4.9GHz + MKKA1 */ 182 MKK9_MKKC = 0xFE, /* Japan UNI-1 even + 4.9GHz + MKKC */ 183 MKK9_MKKA2 = 0xFF, /* Japan UNI-1 even + 4.9GHz + MKKA2 */ 184 185 /* 186 * Regulator domains ending in a number (e.g. APL1, 187 * MK1, ETSI4, etc) apply to 5GHz channel and power 188 * information. Regulator domains ending in a letter 189 * (e.g. APLA, FCCA, etc) apply to 2.4GHz channel and 190 * power information. 191 */ 192 APL1 = 0x0150, /* LAT & Asia */ 193 APL2 = 0x0250, /* LAT & Asia */ 194 APL3 = 0x0350, /* Taiwan */ 195 APL4 = 0x0450, /* Jordan */ 196 APL5 = 0x0550, /* Chile */ 197 APL6 = 0x0650, /* Singapore */ 198 APL7 = 0x0750, /* Taiwan, disable ch52 */ 199 APL8 = 0x0850, /* Malaysia */ 200 APL9 = 0x0950, /* Korea. Before 11/2007. Now used only by APs */ 201 APL10 = 0x1050, /* Korea. After 11/2007. For STAs only */ 202 203 ETSI1 = 0x0130, /* Europe & others */ 204 ETSI2 = 0x0230, /* Europe & others */ 205 ETSI3 = 0x0330, /* Europe & others */ 206 ETSI4 = 0x0430, /* Europe & others */ 207 ETSI5 = 0x0530, /* Europe & others */ 208 ETSI6 = 0x0630, /* Europe & others */ 209 ETSI8 = 0x0830, /* Russia */ 210 ETSI9 = 0x0930, /* Ukraine */ 211 ETSIA = 0x0A30, /* France */ 212 ETSIB = 0x0B30, /* Israel */ 213 ETSIC = 0x0C30, /* Latin America */ 214 215 FCC1 = 0x0110, /* US & others */ 216 FCC2 = 0x0120, /* Canada, Australia & New Zealand */ 217 FCC3 = 0x0160, /* US w/new middle band & DFS */ 218 FCC4 = 0x0165, /* US Public Safety */ 219 FCC5 = 0x0166, /* US w/ 1/2 and 1/4 width channels */ 220 FCC6 = 0x0610, /* Canada and Australia */ 221 FCCA = 0x0A10, 222 FCCB = 0x0A11, /* US w/ 1/2 and 1/4 width channels */ 223 224 APLD = 0x0D50, /* South Korea */ 225 226 MKK1 = 0x0140, /* Japan (UNI-1 odd)*/ 227 MKK2 = 0x0240, /* Japan (4.9 GHz + UNI-1 odd) */ 228 MKK3 = 0x0340, /* Japan (UNI-1 even) */ 229 MKK4 = 0x0440, /* Japan (UNI-1 even + UNI-2) */ 230 MKK5 = 0x0540, /* Japan (UNI-1 even + UNI-2 + mid-band) */ 231 MKK6 = 0x0640, /* Japan (UNI-1 odd + UNI-1 even) */ 232 MKK7 = 0x0740, /* Japan (UNI-1 odd + UNI-1 even + UNI-2 */ 233 MKK8 = 0x0840, /* Japan (UNI-1 odd + UNI-1 even + UNI-2 + mid-band) */ 234 MKK9 = 0x0940, /* Japan (UNI-1 even + 4.9 GHZ) */ 235 MKK10 = 0x0B40, /* Japan (UNI-1 even + UNI-2 + 4.9 GHZ) */ 236 MKK11 = 0x1140, /* Japan (UNI-1 even + UNI-2 + 4.9 GHZ) */ 237 MKK12 = 0x1240, /* Japan (UNI-1 even + UNI-2 + 4.9 GHZ) */ 238 MKK13 = 0x0C40, /* Same as MKK8 but all passive and no adhoc 11a */ 239 MKK14 = 0x1440, /* Japan UNI-1 even + UNI-1 odd + 4.9GHz */ 240 MKK15 = 0x1540, /* Japan UNI-1 even + UNI-1 odd + UNI-2 + 4.9GHz */ 241 242 MKKA = 0x0A40, /* Japan */ 243 MKKC = 0x0A50, 244 245 NULL1 = 0x0198, 246 WORLD = 0x0199, 247 DEBUG_REG_DMN = 0x01ff, 248}; This can be changed in (btw original code as a little hack from apple): ar9300FillCapabilityInfo() ... *(_WORD *)(a1 + 2326) = 141; KPCM Tool to install extensions Check here https://www.firewolf.science/2015/10/kcpm-utility-pro-v5-0-installing-kexts-repairing-permissions-rebuilding-caches-configuring-sip-and-more/ Kernel kext debug here http://www.insanelymac.com/forum/topic/312254-realtek-ethernet-panic-debug-driver-using-xcode-ui/ Atm AR9462 and 9565 were patched using this mehod. I'll stop on 10.11 for the 9565 card as i cant get a stable kernel to work on my amd machine. AR9485, pci168c,32 also working gj dev9565.zip 0036v03.zip1 point

-

I have upgraded Mojave to Catalina. Everything went OK, just the screen was pink (Intel UHD Graphics 630). Downloaded the last version of Lilu and Whatevergreen in Efi/Clover/Kexst/Other and everything goes fine now.1 point

-

1 point

-

1 point

-

Thanks buddy! Testing it out but so far looks good !1 point

-

At the moment, it is quite equivalent to Ozmosis (for our board) but OpenCore has active development while Oz dev has stalled a couple of years ago even tough it was successfully patched by people more saavy than me to allow it to boot the latest macOS; Catalina might be the end of the road for Ozmosis or it might not. The future of Hackintosh is OpenCore.1 point

-

This requires you to modify the C code yourself, then compile it, and the icon has to be found or drawn by yourself!1 point

-

Every Revision of EFI, dsdt and anything else I’ve ever released is on page one buddy1 point

-

It’s on page one bro but sure il add it again to the notice for you.1 point

-

1 point

-

I'll save you some trouble - the AMIBCP method of unlocking the BIOS to show more options on the newer ASRock boards does not work (z390 ASRock itx BIOS 4.40). What you can do is use the 0xE2 MSR unlocking process to set the parameter 'Thunderbolt Force Pwr to 0x1'. Summary steps below1 point

-

While reading your reply I realised the same question was already asked by me some time ago. While searching on the net for a solution I found information about the app SwitchResX, tried it and could indeed disable the TV but even after a reboot the system could somehow see it. The memory clock of the RX kept turning @ 2Ghz. TV is disconnected at the moment and will keep it that way while looking for other possibilities to let the misses watch her series while I use the computer.1 point

-

Hi Follow what @AudioGod says. It's a good solution. One stupid question: I've a MSI Radeon RX580. No IGPU needed, this card supports 4 HDMI ports, so I could use one for monitor and for TV if I want it. Display TV can be disable in macOS.1 point

-

Please how you do that: background and selector! Thanks. I would try it.1 point

-

1 point

-

When installing 10.15.x (or upgrading from 10.14.6), what is the correct value for <key>DefaultVolume</key> in config.plist - so that it auto selects the correct partition during all the multiple reboots that take place?1 point

-

~ ❯ csrutil status System Integrity Protection status: enabled. Took out entry in the config. No issues so far. For those wanting a more pure Hack1 point

-

NDK, I downloaded latest commit and compiled. When running debug version, boot halted with ASSERT error. I've not seen this error before (in fact, I've never seen any errors appear before in this project). Included are some earlier resolution comments as FYI. For this compile, I'd not edited any files and only used your stock icons. I see you added OcClearScreenArea to function PrintOcVersion in OcSimpleBootMenu.c with this latest commit. PrintOcVersion calls AsciiStrCopyToUnicode (from OcAsciiLib.c) and maybe this led to the ASSERT error since OcClearScreenArea is an 'else' statement and String might = NULL. (Trying to be helpful, but I probably don't know what I'm talking about.)1 point

-

After 3 month' s work, now I have successfully added Synaptics Rmi4 F12 support into VoodooI2CSynaptics. Although I2CHID can support this type of touchpad, this kext can provide better support since this kext can provide native rmi4 2d-sensor support but i2chid is running touchpad in Microsoft compatibility mode. It can be loaded and initilize F12 touchpad. After you loaded this new kext you can move curse and use touchpad button. Be caution that this kext haven't been completed and is still buggy. If you have some issues about it, please send an issue in my Github, Thx! My repo: https://github.com/startpenghubingzhou/VoodooI2CSynaptics VoodooI2CSynaptics.zip1 point

-

1 point

-

bios reset button on the io plate but it might not be enough. Most times it is though. if that fails and you don’t want to pull your loop apart then the only other thing you can do is reflash your bios with the latest firmware.1 point

-

Update: I am in the stage of backporting the driver to xcode 4.x to allow for a universal 64-32 bit release, and i am also performing testing, i have still to test the driver on os x 10.8 which is my oldest development platform and i have to still test it on os x 10.6 which is the development target, in the worst case the driver will still work with 10.8 and upwards. I will also need some testers when the driver will be committed and released1 point

-

You do not need to install again after upgrading RAM. Look for 2x8GB 1600MHz DDR3 SoDIMM. After every system upgrade, the patches from your boot stick need to be installed again. For me, Sierra was the last OS working with CS 5.5 without issues. CC should work with Catalina, but I did not try. On a side note, Mac Command-Shift-3 takes a full screenshot. Command-Shift-4 gives you a cross-hair for selecting the area you want to grab.1 point

-

you would have to disable the igpu in the bios to use smbios 1,1 or 19,1 with igpu disabled. there's no way around that one I'm afraid. @decat a rx580 works better with the igpu enabled using 19,1. @channa13 As requested here's a 1,1 version of the OpenCore EFI. AG OC DSDT Free Z390 Master EFI SMBios 1,1.zip1 point

-

Yes sure no problem give me 30mins as I’m just eating my dinner bud side note - if you disable igpu and change shiki too 144 in the boot arguments it’s the same thing but your still running under the correct smbios 19,1 if you do that instead then let me know how it goes for you?1 point

-

It's easily doable but, it will create a delay effect when loading the background image, especially if it's high resolutions screen. I tried, it's kinda annoying effect.1 point

-

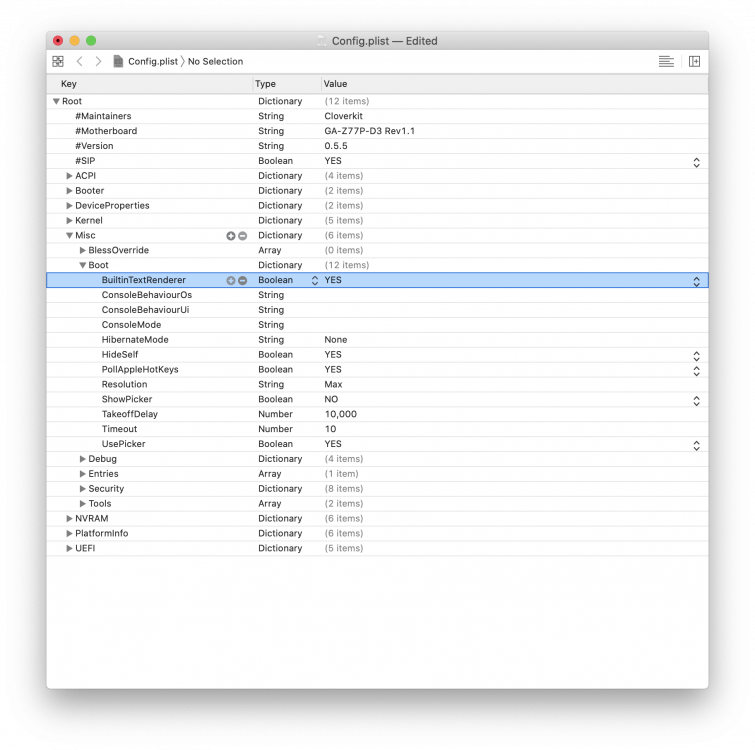

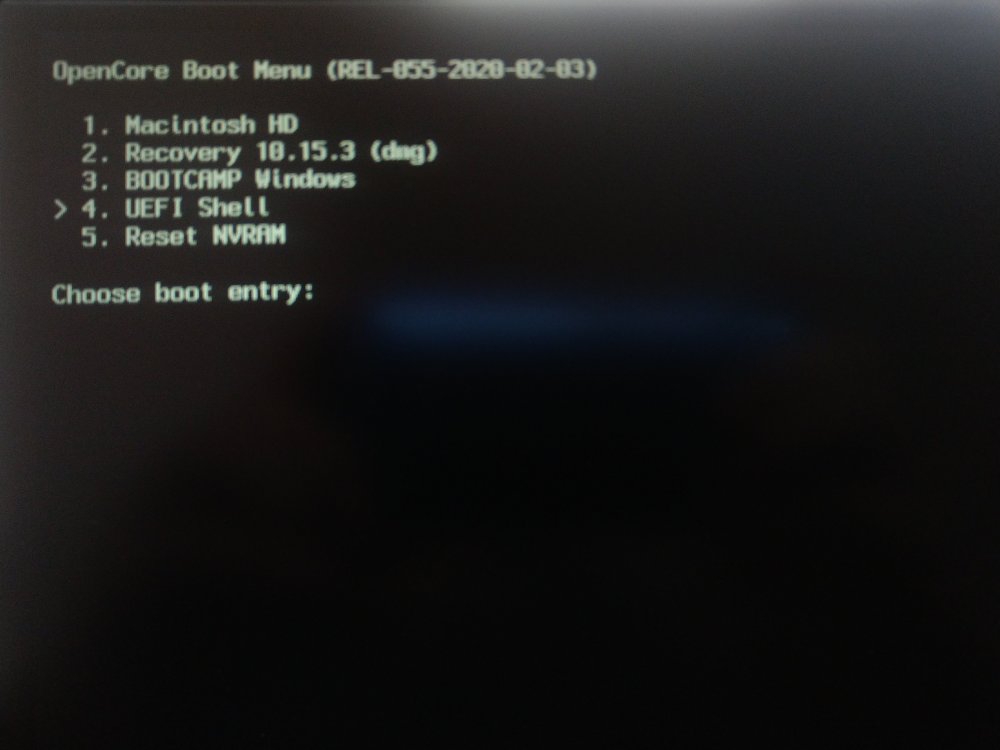

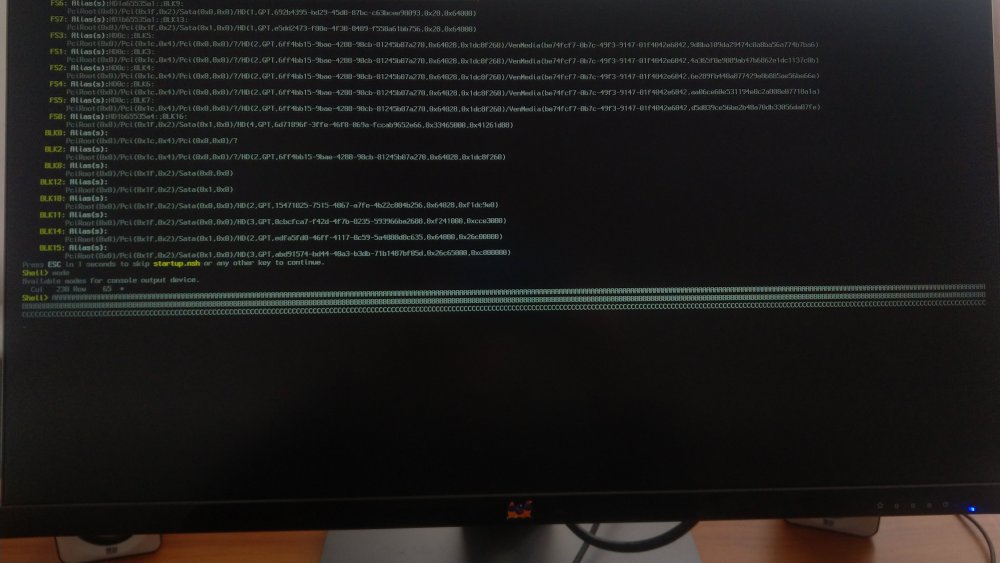

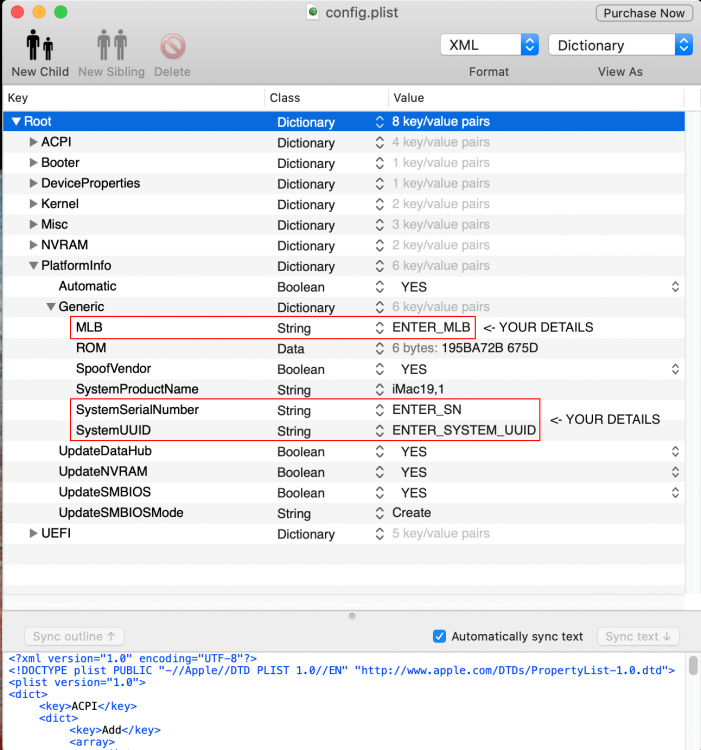

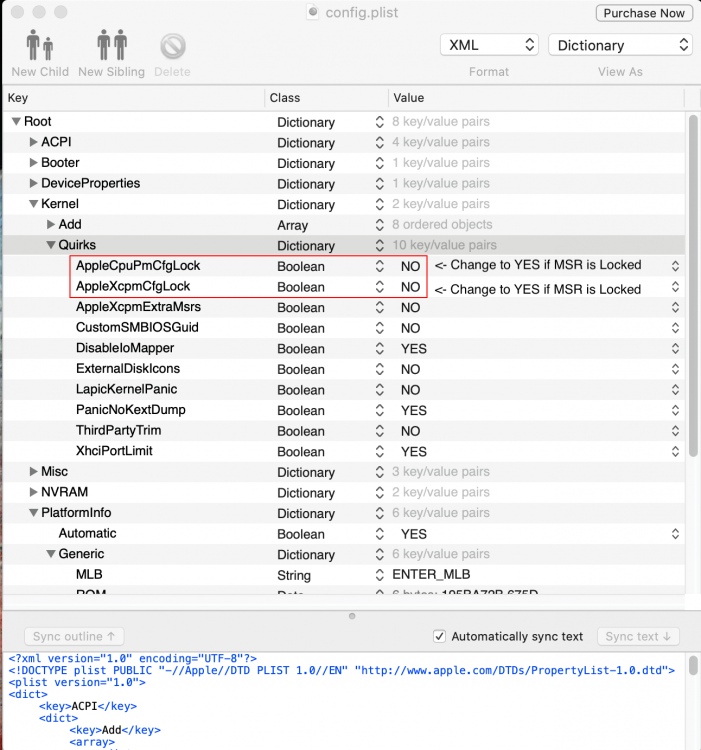

NEW Clover Major EFI, 4th February 2020 (Use With Bios Revision F11c) VERY IMPORTANT NOTICE PLEASE NOTE IT HAS BEEN DISCOVERED THAT THE DRIVER MemoryAllocation.EFI IS MADE FROM THE SAME CODE AS THE FREE2000.EFI DRIVER AND IS POTENTIALLY HARMFUL TO YOUR SYSTEM SO I HAVE DECIDED TO DROP THE DRIVER FROM MY EFIs. You will need to preform a full bios reset by removing all power to the system and then removing the motherboards internal battery for a few minutes then put it all back and load back in your bios profile and continue as normal. If you find your unable to boot up with the new EFI and the IGPU enabled then you can try dropping the IGPU memory from 64mb to 32mb or if that doesn't work you can disable the IGPU and change the boot argument from shikigva=80 to shikigva=144 The EFI and DSDT has now been updated to the my latest version. Changes made include, New DSDT's For bios revision F11c ONLY OcQuirks Revision 13 AppleALC-1.4.6 VirtualSMC 1.11 Clover Updated too Revision 5103 Plus other minor tweaks to the clover config Clover EFI Update - 04/02/2020 - Use with Bios revision F11c Only or Replace with the older F10 DSDT if you don't want to update the bios AG Clover Z390 Master Navi Vega EFI.zip - Vega, Navi (5700, 5700XT), Radeon VII DSDT EFI AG Clover Z390 Master Polaris EFI.zip - RX5XX Polaris DSDT EFI Alternative EFI - OpenCore, No DSDT and Done the way OpenCore intended it 4th February 2020 We have now created a OpenCore EFI done the way the OpenCore Devs intended it to be made, There is no DSDT in use so you can use this EFI on any supported GPU and the SSDTs have been made so they will not be used in any other Operating System apart from MacOS. AG OC DSDT Free Z390 Master EFI.zip - OC Version 0.5.5 DSDT Free, SMBios19,1 (04/02/20) Alternative EFI 2 - N-D-K Fork of OpenCore 4th February 2020 - Use with Bios revision F11c Only or Replace with the older F10 DSDT if you don't want to update the bios. N-D-K OC 055 Navi Vega EFI.zip - Vega 56/64 Navi (5700/5700XT) & Radeon VII DSDT Bios F11c N-D-K OC 055 Polaris EFI.zip - RX Polaris Series DSDT Bios F11c Support on this thread for these EFIs won't be great but @texem and myself will help out where we can. PLEASE NOTE - All bios settings and guide notes are the same for these EFI's and the SMBios is now set to 19,1 For OpenCore and the N-D-K Version Using PlistEdit Pro add your details by modifying the following PLEASE NOTE - These EFIs are setup to be used with your msr Unlocked so make sure you use the F11c Unlocked Profile but if for any reason you can not unlock MSR then just modify following in the OpenCore config.plist : Additional Downloads mb_bios_z390-aorus-master_f11c.zip - Aorus Z390 Master Bios F11c PlistEdit Pro.zip - PlistEdit Pro (use to edit OpenCore) CFG Unlock (MSR) F11c BIOS Profile - The Easy Way I have made this bios profile for you all to use that will unlock CFG on your motherboard making it play alot more friendly with the NVRam. It also has all the bios settings listed on this guide pre done and saved onto the profile. F11c MSR Unlocked Profile.zip - Use with Bios Revision F11c ONLY 1 - Download the profile and save it to a USB Key 2 - Go into the bios, 3 - Load the profile, 4 - Save and exit 5 - Go straight back into the bios and save your bios to a new profile and name it Default CFG Unlocked or something like that. 6 - Boot back into Catalina go into your clover config and under Kernal and Kext Patches Uncheck KernalPM 7 - Save the changes and then restart and your done, your motherboard will now be CFG (MSR) Unlocked PLEASE NOTE - If you reset the bios or load bios defaults it will clear the Unlock making CFG Locked again. 1 point

-

1 point

-

The new version is still work in progress, i am working on some small things and also to fix some bugs, but the new boot arg has been implemented and tested just yesterday1 point

-

I thinking boot arg is not bad idea. I'm ready to test your build with this fixes on my the hackintosh configuration. Main problem with your previously released drivers - noises on the youtube videos. No any other issues. I don't use creative card for input sounds, only for playback.1 point

-

On Asus Logo press and hold without releasing. To release when you will see Apple Logo. Show screenshot Input and Drivers sections in config.plist1 point

-

About the cracking issues it turns out that in some cases the n_frames multiplyer solves the issue, but in some other cases it makes tha issue appear, for example in my own pc just having it makes the cracking issue appear, wile in case of @BiOM1 it just solves it, so i was just thinking about introducing a boot arg to enable or disable the n_frames multiplyer and to specify it's value, so it's possible to play with it and find the correct value to solve the issue for each user without requireing diver ricompilation, it should be pretty easy for me to implement it because i have already implemented something similar for custom sample rates in the driver. I need the opinion of both of you guys @BiOM1 @>Alejandro1 point

-

The EFI released works perfectly provided you set up your system as he suggested. Get a proper macOS installer without errors. This is crucial as people use all sorts of dumb ways to make the stick, either pulling an incompatible version or an assortment of errors that either fubar the install process or leave you with a non-working system. Stop and take a step back. Make a USB installer on a real macOS running the latest OS. Ensure it's good and error free. Update your BIOS to the latest revision (F12d for the Pro and F12c for the Pro WIFI, both work with this EFI). Set up the BIOS properly. You need to first enable the dGPU, save settings and reboot, then go right back into the BIOS and finish setting it up. Only then will it list the following settings: • Settings -> IO Ports -> DVMT Pre-Allocated -> 64M • Settings -> IO Ports -> DVMT Total GFX0-Allocated -> 256M • Settings -> IO Ports -> Aperture Size -> 256MB That's mostly it. Unplug all your hardware that's not necessary. If you have some kind of radiator cooling system, then you may need to do some fiddling as there are known issues with lots of fancy cooling (by fancy I mean coming from traditional air cooling like the Notcua DH-14). macOS doesn't support anything other than traditional air cooling systems (fan + heatsink). You're throwing up a ton of info, way too much. I get what you're trying to do, but this EFI is bulletproof. You just toss in your EFI partition and you're good. Truly.1 point

-

Please share what exactly did you replaced. For example I see patch 0 replaces GPRW in _PRW but can't understand what exactly. Is it Method (_PRW, 0, NotSerialized) { GPRW(0x6d, 0x04) replaced with Method (_PRW, 0, NotSerialized) { GPRW(0x00, 0x00) ? Is there any tables of acpi commands and corresponding bytecodes/instructions? Thank you!1 point

-

Hi, All! After some weeks testing i'm ready present my version of kx project drivers for OSX. Driver tested on my hackintosh with Creative Audigi 2 on OSX Catalina 10.15.2 . Based on ITzTravelInTime sources (99.9%) with some fixes for actual bugs. Many thank to ITzTravelInTime, Alejandro and all other developers for this great drivers! The most important fix - no sound defects on Youtube videos :) Sorry for my ugly english kx-audio-driver.zip1 point

-

And Please don't write anything here that are not related to the modification of this fork.1 point

-

The issue has been fixed. The board's ME firmware was corrupt. Modding the BIOS to fix ME in conjunction with directly flashing the non-corrupt firmware to the ME region using FTK did the trick. Note that Windows was used for the fix. What was the issue? macOS currently expects a functioning ME device (HECI/IMEI) for Intel graphics to fully load. Because the firmware was corrupt, the kexts only loaded halfway and kextd stalled. On Windows, the ME device was "disconnected" in Device Manager. This is why even with IMEI in the IOReg, correct Clover settings and FramebufferAzul and HD5000Graphics kexts loaded in kextstat I could not get QE/CI, or even a proper graphics output. Once the firmware was restored, the ME coprocessor booted completely and the hack gets full acceleration now. For future note: should this method fail, the only option is to buy a new preflashed BIOS chip. Proceed with care. after.BMP before.BMP1 point

-

Oh yes, ^^^ that too. Do both things. I should read everything besides seeing one word, lol.1 point

-

1 point

-

First of all you don’t have to be a know-it-all or rude. Also you don’t need to dictate about what we discuss here or what boot loader we use and why. I like to think that people of all hackintosh experience levels are welcome to join this conversation and discuss since we are sharing the same motherboard as well as the hackintosh-fever. The boot loader we’ ll use is also our choice and everyone can switch between OpenCore and Clover whenever they want, since @AudioGod and @texem have made it possible with their rock solid variants. Last but not least, it’s not a matter of wondering why it doesn’t work on Clover or OpenCore. I’ve been having issues with disabling the Kernel Power Management Patches on an MSR UNLOCKED configuration which replicate on both Clover and OpenCore and that’s what we are discussing about, since @Pieroman read about these issues and wanted to know more.0 points

.thumb.jpeg.7082d67b3394c9399e80144027a7b397.jpeg)