Leaderboard

Popular Content

Showing content with the highest reputation on 04/15/2018 in all areas

-

Would be a great idea to update it. If anyone have the complete knowledge about Clover, we can create a "second" Wiki here in IM. What do you think?3 points

-

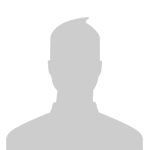

Guys this package: HWSensors-3_r118.pkg.zip contains an improved version of HWMonitorSMC2.app: - new SMART core made in swift (world first?) that can read s.m.a.r.t. attributes from ATA and finally from NVMe disks - on right click over any rows (not all but most of it) show detailed info about: CPU (brand string, system usage) RAM S.M.A.R.T. attributes with detailed informations about your disks (BSD name, vendor name, serial etc.), Battery (laptops) with capacity, max capacity, cycle count, temperature etc. (anyway not with VoodooBattery but works with Rehabman's kext or in a real mac) SYSTEM with info about processes, threads and more. POWER (if supported), with info about cpu limit, thermal level etc. Please show a screen shot about S.M.A.R.T on SATA and NVMe because I worked hard on this. Big thanks goes to @fabiosun for tens and tens of tests made who helped me a lot debugging smart on mechanical and nvme drives (which I did not own). Thanks goes also to SystemKit.framenwork, now embedded into the project and smartmontools for the reverse engineering that make possible acquire smart datas for NVMe drives on macOS! TODO: - do a better layout of the datas showned when you right click fixed - find gpu information somehow @Slice, soon (tonight) I'll commit those changes, just waiting some tests here EDIT commited2 points

-

the sb0570 is the audigy se which is not compatible with this driver, you have to own sound cards based on the 10k1 or 10k2 or similar chipsets to work with this driver, yours uses a totally different architecture, but if you want to test it, compatible sound cards like sopund blaster live are cheap to get and compatible, for pcie you can use the sound blaster audigy rx2 points

-

Hi ITzTravelInTime. I am new to hackintosh world. I have a Sound Blaster Audigy SE SB0570. I tried your driver and it is not working, as expected. I would like to help you in some way, I am a developer. Please fell free to ask me for tests or anything. Thanks for your effort!2 points

-

If Clover is going to GitHub, having a GitHub wiki would be easier for people to update, and translate.2 points

-

I have 3 Radeon HD 5450 testing in HighSierra and its working like Sierra no difference here2 points

-

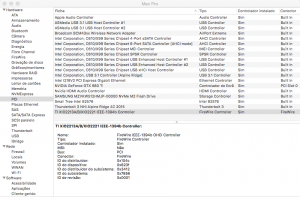

-Donations with PayPal https://tinyurl.com/r2bvzm7 -Donations with Bitcoin 33HeGCuCSh4tUBqdYkQqKpSDa1E7WeAJQ3 -Donations with PicPay @danielnmaldonado Nehalem, SandyBridge, IvyBridge, Haswell, Broadwell https://www.olarila.com/topic/5794-guide-install-macos-with-olarila-image-step-by-step-install-and-post-install-windows-or-mac/ Skylake, Kabylake and Coffeelake is here https://www.olarila.com/topic/5794-guide-install-macos-with-olarila-image-step-by-step-install-and-post-install-windows-or-mac/ Install MacOS with Olarila Image, Step by Step, Install and Post Install https://www.olarila.com/topic/5794-guide-install-macos-with-olarila-image-step-by-step-install-and-post-install-windows-or-mac/ First... ***Update bios to last available version!*** If you need a full patched DSDT... -Extract tables with F4 key in Clover boot screen! -Run it and send me files! RunMe.app Installation --Create a bootable copy of macOS Sierra / High Sierra / Mojave https://github.com/chris1111/Create-Install-Media/releases --Install Clover in USB stick https://github.com/CloverHackyColor/CloverBootloader/releases --Replace with my Clover folder https://tinyurl.com/ybr968w3 --Install Sierra/High Sierra and boot into system! Post Installation --Install Clover and replace with my folder https://tinyurl.com/ybr968w3 --Reboot and activate video! Bingo! Now you need a fine tune! DSDT time! --DSDT Patches -FIX ERRORS AND WARNINGS -HPET -SATA -DMAC -SLPB -DARWIN -LPC -XHCI -PLUGIN TYPE -XXXX to HDEF -HDEF -RTC -IRQs -SBUS -BUS1 -MCHC -ALS0 -SHUTDOWN -LAN -USBX -PMCR -EC -PNLF -HDMI --Power Management - 1 Generation Intel Processors, use Generate P and C States in config.plist - 2 and 3 Generations Intel Processors, Generate SSDT with Piker script and drop CpuPm and Cpu0Ist SSDTs ssdtPRGen.command.zip Credits-https://github.com/Piker-Alpha/ssdtPRGen.sh - 4 Generation+ Intel Processors, use PluginType=1 in DSDT, SSDT or Clover config.plist for check Power, Frequency, Temperature and Utilization, use it Install Intel Power Gadget.pkg.zip --Brightness Install .app, select the required permission and reboot. Work in F1 / F2 keys! NativeDisplayBrightness.app.zip https://github.com/Bensge/NativeDisplayBrightness/releases *in some cases .app don't work, check patches in config.plist inside Clover folder Post Install --Clover https://sourceforge.net/projects/cloverefiboot/files/Installer/ --AUDIO Use DSDT + AppleAlc --install Lan driver by Mieze -Atheros http://www.insanelymac.com/forum/files/file/313-atherose2200ethernet/ -Intel http://www.insanelymac.com/forum/files/file/396-intelmausiethernet/ -Realtek http://www.insanelymac.com/forum/files/file/88-realtekrtl8111-binary/ --Links -FakeSMC https://bitbucket.org/RehabMan/os-x-fakesmc-kozlek -Audio https://github.com/vit9696/AppleALC http://www.insanelymac.com/forum/topic/314406-voodoohda-289/ -USB https://bitbucket.org/RehabMan/os-x-usb-inject-all/downloads It's time to Rock -Credits and thanks to the old and new people in the community who developed patches, kexts and bootloaders! Apple, Slice, Kabyl, usr-sse2, jadran, Blackosx, dmazar, STLVNUB, pcj, apianti, JrCs, pene, FrodoKenny, skoczy, ycr.ru, Oscar09, xsmile, SoThOr, RehabMan, Download-Fritz, Zenit432, cecekpawon, Intel, Oracle, Chameleon Team, crazybirdy, Mieze, Mirone, Oldnapalm, netkas, Elconiglio, artut-pt, ErmaC, Pavo, Toleda, Master Chief and family, bcc9, The King, PMheart, Sherlocks, Micky1979, vit9696, vandroiy2013, Voodoo Team, Pike R. Alpha, lvs1974, Austere.J, CVad and many, many, many others! We're all here to have fun and learn from each other!1 point

-

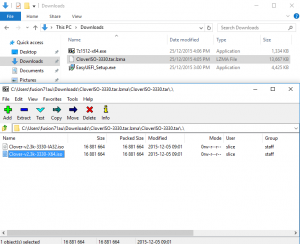

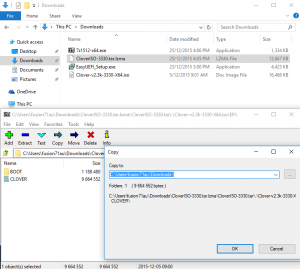

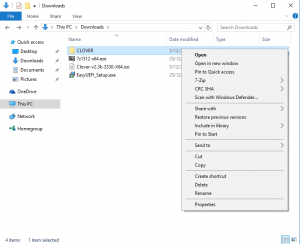

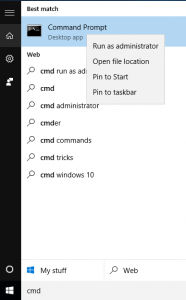

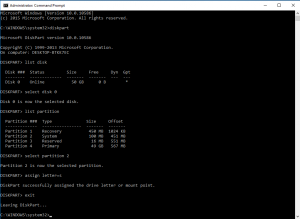

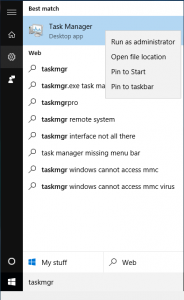

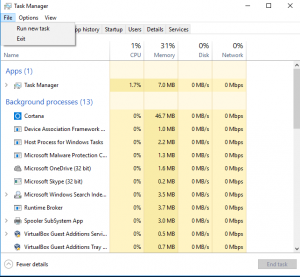

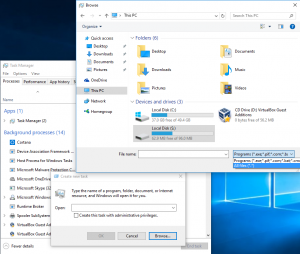

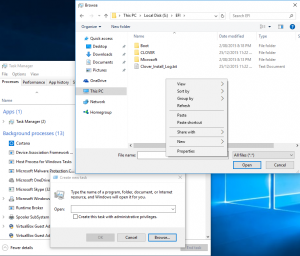

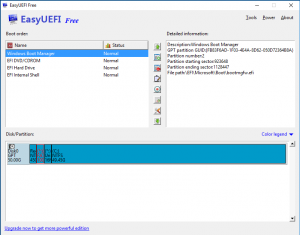

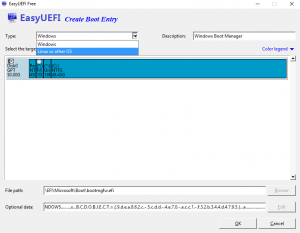

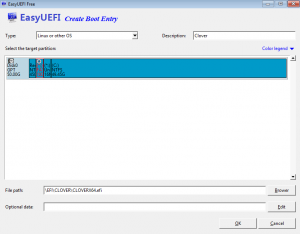

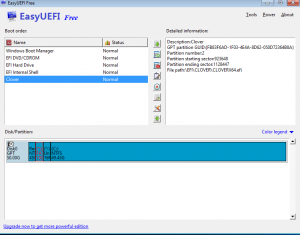

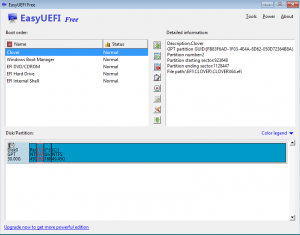

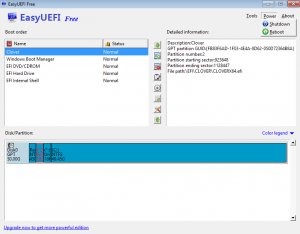

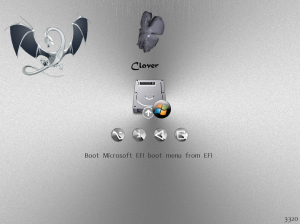

Manually install Clover for UEFI booting and configure boot priority with EasyUEFI in Windows This tutorial will show how to manually install Clover in the EFI system partition of a pre-existing install of UEFI Windows. In the process, you will also learn how to mount the EFI partition and add Clover as a UEFI boot option (using the EasyUEFI program) in Windows. Prerequisites 1. CloverISO from Sourceforge. 2. 7-Zip for Windows 3. EasyUEFI 4. Existing UEFI install of Windows X64 (7,8,8.1 or 10) Obtain Clover 1. Download the CloverISO.tar.lzma file from Sourceforge and open the file with 7-Zip. 2. Extract the Clover subfolder to your \Downloads with 7-Zip. 3. Copy the Clover folder by right clicking on its icon in Windows File Explorer. Mounting the EFI System Partition and installing Clover 1. Open an administrative command prompt by clicking the Windows start button, typing cmd and right clicking on the search result as shown below... 2. Type the following commands, followed by <Enter> after each line: diskpart list disk select disk # (where # is the disk number of the disk with UEFI Windows) list partition select partition x (where x is the partition number of the EFI system partition. By default, it is usually the 100MB second partition) assign letter=s exit 3. Open Windows Task Manager as administrator by clicking the Windows start button, typing taskmgr and right clicking on the search result as shown below... 4. Click Run new task 5. Click Browse and in the Browse window, navigate to the EFI folder in the System Partition (which is mapped to drive S:) and also select "All files" from the drop down menu... 6. Right click inside the EFI folder to "paste" the Clover folder we downloaded earlier. If necessary, you can make edits to Clover's default config.plist with Wordpad or add OSX kexts like FakeSMC into the \kexts\other folder while still in the Task Manager browse window. For UEFI booting into OSX, you will most likely need the OsxAptioFix2Drv-64.efi or OsxAptioFixDrv-64.efi driver in EFI\CLOVER\drivers64UEFI (copy from the \CLOVER\drivers-Off\drivers64UEFI folder). 7. Quit Task Manager. Add Clover as a UEFI Boot Option using the EasyUEFI Program 1. Open EasyUEFI and click on the small icon with the plus sign (second from top) to add a new entry. 2. In the Create Boot Entry Window, choose "Linux or other OS" as the entry type, click to select the EFI System partition as the target and browse to the CLOVERX64.efi file (file path \EFI\CLOVER\CLOVERX64.efi) as shown below... 3. Type Clover in the Description field then the OK button. 4. You will now see the new Clover entry on the main GUI of EasyUEFI. Click on the entry and then click the small up arrow icon to move Clover to the top so it will get priority over the Windows Boot Manager on boot up. Note on this screen, you can also delete/edit/disable boot entries or move them down the boot order. 5. Click the power menu and select reboot to restart your system (use your system's boot device selection key to choose the drive with CLOVER installed if necessary eg F12 for Gigabyte motherboards, F8 for ASUS motherboards, F11 for ASrock motherboards) ---> will now be presented with the Clover Main Menu GUI to boot Windows (or OSX). Enjoy and Good Hack !1 point

-

1 point

-

Hi there, time for my first guide after asking so many things Updated for newer Clover versions and with additional instructions for more apps: gdisk and RU. So what may be overlooked sometimes in the whole boot loader discussion is the ability of UEFI to do more than just loading an OS. This is why I see ".efi" files as "apps" because in fact they just are, built on a special kind of API: UEFI. So, you can actually do stuff like editing, diagnosing, testing certain stuff at the lowest possible system level without booting to any OS. DISCLAIMER: Use this guide at your own risk! For educational purposes only! Should do not any harm, but remember you are dealing with rather low level stuff. But at least for me everything went flawless. Prerequisites: Working clover installation Clover Configurator or some app to edit the config.plist 1) Memtest This is how to install the UEFI version of Memtest with Clover: Download memtest, I used this link: Image for creating boot-able USB Drive Open the archive by double clicking on it. Mount the file memtest86-usb.img within by double clicking again. Now, you should see a folder named EFI in this volume, containing a folder BOOT. Open it. The files containing it are the actual app, in 32 and 64 bit versions. Think in almost all cases we want to use the 64 bit version. Now, mount your EFI partition, using Clover configurator. Create a folder named MemTest86 in the EFI folder on your main drive. Copy all files in the EFI/BOOT folder from the mounted image to your newly created folder. That ends the basic setup! Now, we add the correct Menu entry to the clover boot menu, so that we can actually start this app. Get into clover configurator, open your standard config.plist from your boot drive and go to the GUI section. Under "Custom Entries", add an entry like this: Please note while the path you enter is not case sensitive, you must make sure you use the backslash "\" for entering paths, and not a slash. So basically what we do is tell clover where it can find the app, give it a name, and tell clover it is a "Windows" app. Note: with older Clover versions we had to set this to "Linux", but for now "Windows" is the setting that works. If you prefer to do a manual config, add this entry to your config.plist, under GUI/Custom/Entries: <dict> <key>CustomLogo</key> <true/> <key>Disabled</key> <false/> <key>FullTitle</key> <string>MemTest86</string> <key>Hidden</key> <false/> <key>Ignore</key> <false/> <key>Image</key> <string>\EFI\CLOVER\themes\Icons\os_mint.png</string> <key>Path</key> <string>\EFI\MemTest86\BOOTX64.efi</string> <key>Type</key> <string>Windows</string> <key>VolumeType</key> <string>Internal</string> </dict> Now, save and reboot and you should see the newly created entry. Note that I also used a custom Icon - this is optional - in case you don't you will just see a generic windows icon instead: And this is how it looks like: PS: also noticeably faster and you get also more features with this version than with the older version, for example it does now write a log file. For more Information, see: http://www.passmark.com/forum/showthread.php?4315-Memtest86-Version-5-Beta-%28Pure-UEFI%29 2) gdisk Another app you can use is the UEFI version of gdisk (aka GPT fdisk), which you can use to edit and change your partitions. Warning! Install and use this app at your own risk! If you do something wrong here you might nuke your drive(s), so only use that if you know what you are doing. This is how to do it (even easier): Download here: https://sourceforge.net/projects/gptfdisk/files/gptfdisk/1.0.1/gdisk-binaries/gdisk-efi-1.0.1.zip/download Mount your EFI partition Unzip the file and copy the resulting folder to your EFI Folder, so your path goes like this "/Volumes/EFI/EFI/gdisk-efi" Get into clover configurator, open your standard config.plist from your boot drive and go to the GUI section. Add an entry like this: If you prefer to do a manual config, add this entry to your config.plist, under GUI/Custom/Entries: <dict> <key>CustomLogo</key> <false/> <key>Disabled</key> <false/> <key>FullTitle</key> <string>GDisk</string> <key>Hidden</key> <false/> <key>Ignore</key> <false/> <key>Image</key> <string></string> <key>Path</key> <string>\EFI\gdisk-efi\gdisk_x64.efi</string> <key>Type</key> <string>Windows</string> <key>VolumeType</key> <string>Internal</string> </dict> When everything went OK you should see this after selecting the respective entry in Clover: 3) RU I recently found one more app that might be interesting to some, and thats "Read Universal" or in short "RU". This is a tool that enables you to debug your BIOS and read (and modify!) every imaginable data, including UEFI variables, ACPI Tables etc. Warning, again! I think blindly messing around with this app is even more dangerous, but on the other hand it gives you access to a lot of potentially interesting stuff. Download here: http://ruexe.blogspot.de/ The next steps are basically the same as above so make a folder in your EFI partition, copy the .EFI files and make another custom entry in your config.plist Here are some screens: So this is what you also can do with UEFI and clover. I am curious which other useful applications might exist! Anybody who knows, maybe post it here?1 point

-

Posta se pui la cartella Clover funzionante quella con impostazioni migliori al momento x il tuo HW ..... Al notebook della mia ragazza la Ethernet funziona solo se installo in S\L\E FakePCIID_BCM57XX_as_BCM57765.kext con lilu e FakePCIID in other in Clover .... Puoi provare cosi , non si sa mai ....1 point

-

Oh I see. Well, thanks for the reply. I have a P8Z77-V PRO motherboard and the Realtek onboard is not working, so I bought a cheap sb0570. But I will try to change for a compatible one, like the pcie SB Audigy Rx.1 point

-

Are you booting with UEFI or Legacy? I am guessing that the boot sequence changed from first Windows drive to first Clover drive. You need to get to the BIOS and update the boot priority. Another way to do this is to update Clover to autoboot to Windows as default. You could use Clover Configurator to do that. If you are going down this path, select the System Reserved partition as boot on MBR, not the partition with Windows. Hope it helps.1 point

-

1 point

-

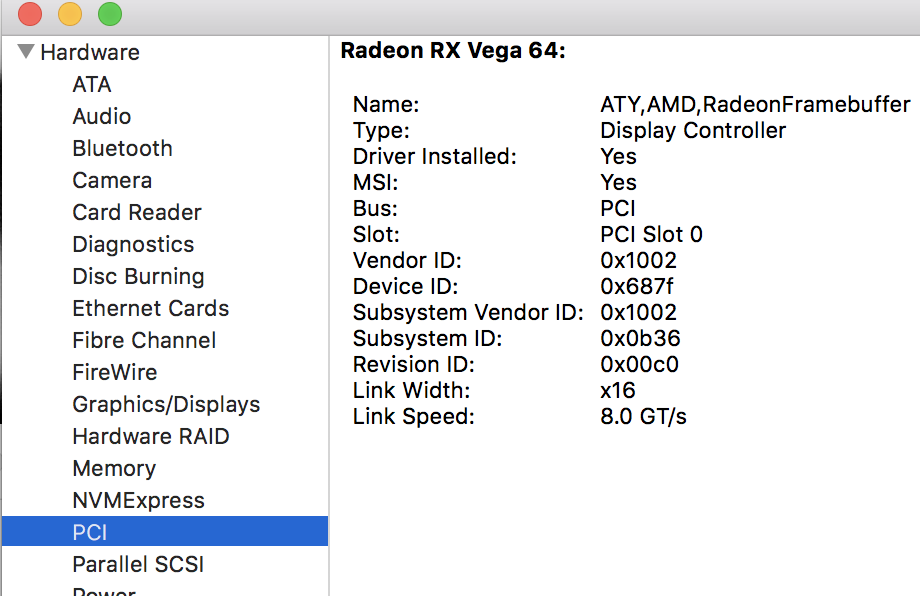

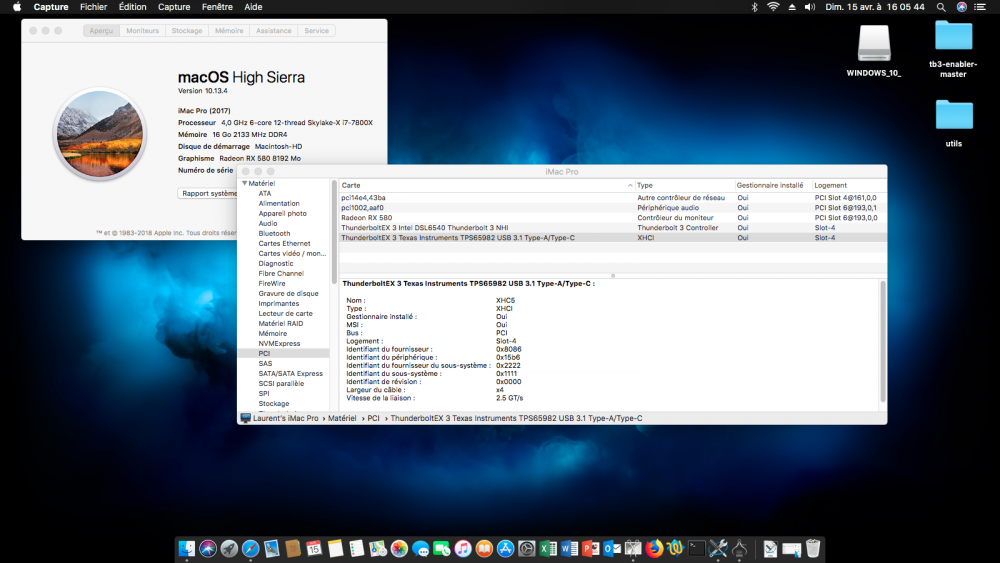

Thanks Matthew82 ! : After a week of severals issues : 1/ Bios recommended parameters + Pci devices set as Legacy 2/ I added arbitrary lines on my config.plist 3/ I created my own SSDT What is working : - Hot plug USB or HDD pluged on USB 3.1 or USB C : eject and re-plug OK Not working ( working in Windows 10 ) - Display sreen connected on USB C1 point

-

Sposta pure i kext in 10.13 poi invece di un riavvio spegni il pc e avvialo. Controlla tutto, la rete dovrebbe esserci Per l’audio devi selezionare l’uscita giusta in preferenze di sistema probabilmente.1 point

-

Devi scegliere sempre quella col nome del tuo hdd. Gli altri li faremo sparire. Finché farai il boot dalla penna avrai sempre quello install sierra1 point

-

you're most welcome i would really like if all the inputs and outputs working without any problem1 point

-

1 point

-

Hello, what about USB3? I have Z620 but have errors only with USB.1 point

-

Mio fratello ha una Mobo praticamente identica con quello che ti ho passato dovrebbe funzionarti tutto. ti mancherà fare un ssdt per il pm1 point

-

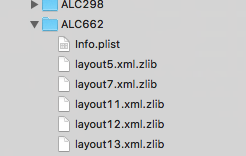

you should delete voodoohda.kext and applehdadisabler.kext as youve got applealc.kext which is the best option. also the ioreg you sent was without voodoo patches. personally i think you should do a fresh install and keep the clover setup. as youve got a lot of stuff you shouldnt have.1 point

-

1 point

-

Andiamo per passi: - Kext. Primo, decidi dove metterli, o other o 10.13 non in entrambi. Secondo, non si mettono a caso; di quelli che hai messo in other l'unico utile è FakeSMC gli altri sono inutili se non nocivi. Per la rete non ne hai brincato uno, tu hai una Broadcom BCM57781, voodoops2 è per per laptop, usbinjectall probabilmente inutile. - Config. Questo deve rispecchiare l'hardware metterne uno a caso non è buona cosa. il tuo per esempio ha un SMBIOS (incompleto) per Haswell Imac14,2 quando quello corretto è 13,2. Continuando, sostituisci il config con quello allegato e d'ora in poi usa/modifica sempre questo. Cancella i kext in other e in 10.13 aggiungi al FakeSMC quelli contenuti in nello zip allegato (compresa la cartella Post-Install). Riavvia il pc e alla schermata di Clover premi un paio di volte F4 e attendi una 30ina di secondi prima di fare il boot, tu non vedrai accadere niente ma questa operazione estrae le tabelle ACPI originali( DSDT e SSDT) che troverai nella cartella EFI/CLOVER/ACPI/origin che devi postare zippata. Controlla che sia popolata di file altrimenti devi ripetere l'operazione Kext in 10.13.zip config.plist 2.zip1 point

-

Prova le Kext in Clover mettile SOLO in Other x ora , e lascia solo quelle essenziali AGGIORNATE x 10.13.4 , puoi specificare se hai installato in UEFI o Legacy HFS o APFS??? E se usi Nvidia o VGA integrata nella CPU Intel ... CLOVER Prova.zip1 point

-

Last login: Sun Apr 15 09:42:01 on console iMac-di-Fabio:~ fabio$ diskutil list /dev/disk0 (internal, physical): #: TYPE NAME SIZE IDENTIFIER 0: GUID_partition_scheme *250.1 GB disk0 1: EFI EFI 209.7 MB disk0s1 2: Apple_HFS macOS Sierra 249.2 GB disk0s2 3: Apple_Boot Recovery HD 650.0 MB disk0s3 /dev/disk1 (internal, physical): #: TYPE NAME SIZE IDENTIFIER 0: GUID_partition_scheme *120.0 GB disk1 1: EFI EFI 209.7 MB disk1s1 2: Apple_APFS Container disk2 119.8 GB disk1s2 /dev/disk2 (synthesized): #: TYPE NAME SIZE IDENTIFIER 0: APFS Container Scheme - +119.8 GB disk2 Physical Store disk1s2 1: APFS Volume macOS High Sierra 97.6 GB disk2s1 2: APFS Volume Preboot 21.9 MB disk2s2 3: APFS Volume Recovery 517.8 MB disk2s3 4: APFS Volume VM 20.5 KB disk2s4 iMac-di-Fabio:~ fabio$ /Users/fabio/Downloads/smarter disk0 Medium Type: HDD Protocol: SATA Location: Internal Temperature: 55834574872C° S.M.A.R.T. check disk0: IOCreatePlugInInterfaceForService() failed with error "IOKit Common: no resource" S.M.A.R.T. status: not capable S.M.A.R.T. data (512 bytes): UInt8 smartdata[] = { 0x0A, 0x00, 0x01, 0x0F, 0x00, 0x6D, 0x63, 0x9D, 0x6E, 0x4F, 0x01, 0x00, 0x00, 0x00, 0x03, 0x03, 0x00, 0x62, 0x61, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x04, 0x32, 0x00, 0x5D, 0x5D, 0x26, 0x1D, 0x00, 0x00, 0x00, 0x00, 0x00, 0x05, 0x33, 0x00, 0x64, 0x64, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x07, 0x0F, 0x00, 0x54, 0x3C, 0x42, 0x9D, 0x32, 0x0E, 0x00, 0x00, 0x00, 0x09, 0x32, 0x00, 0x5F, 0x5F, 0x28, 0x12, 0x00, 0x00, 0x00, 0x00, 0x00, 0x0A, 0x13, 0x00, 0x64, 0x63, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x0C, 0x32, 0x00, 0x60, 0x60, 0x78, 0x11, 0x00, 0x00, 0x00, 0x00, 0x00, 0xBB, 0x32, 0x00, 0x01, 0x01, 0x68, 0x01, 0x00, 0x00, 0x00, 0x00, 0x00, 0xBD, 0x3A, 0x00, 0x60, 0x60, 0x04, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0xBE, 0x22, 0x00, 0x4C, 0x35, 0x18, 0x00, 0x13, 0x18, 0x00, 0x00, 0x00, 0xC2, 0x22, 0x00, 0x18, 0x2F, 0x18, 0x00, 0x00, 0x00, 0x0D, 0x00, 0x00, 0xC3, 0x1A, 0x00, 0x72, 0x3F, 0x81, 0xC7, 0x89, 0x03, 0x00, 0x00, 0x00, 0xC5, 0x12, 0x00, 0x64, 0x64, 0x06, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0xC6, 0x10, 0x00, 0x64, 0x64, 0x06, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0xC7, 0x3E, 0x00, 0xC8, 0xC8, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0xC8, 0x00, 0x00, 0x64, 0xFD, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0xCA, 0x32, 0x00, 0x64, 0xFD, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x82, 0x00, 0xAE, 0x01, 0x00, 0x5B, 0x03, 0x00, 0x01, 0x00, 0x01, 0x5C, 0x02, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x04, 0x03, 0x03, 0x03, 0x02, 0x03, 0x03, 0x03, 0x03, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x01, 0x5A, 0xE1, 0x52, 0x0F, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0xD6, 0x93, 0xC0, 0xF9, 0xFC, 0x01, 0x00, 0x00, 0x06, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x5A, 0xE1, 0x52, 0x0F, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x02, 0x00, 0x01, 0x00, 0x00, 0x00, 0x0F, 0x00, 0x00, 0x00, 0x40, 0x77, 0xDC, 0x81, 0x03, 0x00, 0x00, 0x00, 0x02, 0x9C, 0x01, 0x00, 0x00, 0x00, 0x00, 0x00, 0x27, 0x12, 0x00, 0x00, 0x00, 0x00, 0x01, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x25 } iMac-di-Fabio:~ fabio$ diskutil info disk0 Device Identifier: disk0 Device Node: /dev/disk0 Whole: Yes Part of Whole: disk0 Device / Media Name: MAXTOR STM3250310AS Volume Name: Not applicable (no file system) Mounted: Not applicable (no file system) File System: None Content (IOContent): GUID_partition_scheme OS Can Be Installed: No Media Type: Generic Protocol: SATA SMART Status: Verified Disk Size: 250.1 GB (250059350016 Bytes) (exactly 488397168 512-Byte-Units) Device Block Size: 512 Bytes Read-Only Media: No Read-Only Volume: Not applicable (no file system) Device Location: Internal Removable Media: Fixed Solid State: No Virtual: No Hardware AES Support: No iMac-di-Fabio:~ fabio$1 point

-

Hi, @MaLd0n I hope you have some rest with my Beer present! :)) Thank you for always helping me buddy! So I just updated Bios F6 now. And just I said I have some issue about shutdown with SSDT-TB3 Please see my file. I pushed f4 in clover. So this one is good to go. https://www13.zippyshare.com/v/TUb7L1wR/file.html Thank you!1 point

-